endpoint intelligence

# **Apollo3 Family** Power Consumption Optimization & Technical Details

August 2022

endpoint intelligence

# Power Consumption Optimization

- Apollo3 sleep modes are very flexible.

- Entering Normal or Deep Sleep does not automatically change the clock source for timers, nor does it stop or disable any peripherals or interrupt sources.

- Configure the peripherals and GPIO in the desired way and they will continue to operate in normal or deep sleep. Keeping peripherals active will result in higher deep sleep current, so for lowest power deep sleep, all peripherals not actively in use should be powered down.

- It is straightforward to enter sleep modes:

- am\_hal\_sysctrl\_sleep(AM\_HAL\_SYSCTRL\_SLEEP\_DEEP);

- am\_hal\_sysctrl\_sleep(AM\_HAL\_SYSCTRL\_SLEEP\_NORMAL);

- Any Apollo3 interrupt can be used as a wake trigger from normal or deep sleep.

- Common wake interrupt sources used in deep sleep include:

- GPIO, Ctimer, Stimer, RTC Alarm, Comparator, ADC Window compare, I2C/SPI slave write, FIFO threshold interrupts for any serial interface, etc.

- The Binary counter example project is a good example of using LFRC as Timer count source and going to deep sleep with that timer running. The timer then generates a periodic wake interrupt.

- Keeping timers running from either XT or LFRC add <100nA to deep sleep current (plus the current of the clock source, which is ~300nA for XT and <100nA for LFRC).</li>

- All Apollo3 GPIO can be used as a wake source.

- To configure a GPIO as a wake source, enable the interrupt for that GPIO. Please see the deepsleep\_wake project for simple example of this.

- All GPIO have configurable interrupts, and any GPIO that has interrupt enabled will wake the MCU from deep sleep upon GPIO interrupt.

- All Timers can be used as a wake source.

#### Power Optimization: Tips

- The HFRC will be stopped automatically when entering deep sleep UNLESS there are peripherals or timers running that need HFRC.

- For lowest power deep sleep, any timer or peripheral that is configured to use HFRC should be stopped before entering Deep Sleep.

## Power Optimization: Tips

- On Apollo3, peripherals such as UART, IOM (SPI/I2C master), IOS (SPI/I2C Slave), MSPI, ADC, and PDM all have a peripheral power enable/disable bits.

- All of these peripherals start powered off. This power-gates the peripheral for minimum leakage in deep sleep.

- Each of these peripherals must be power-enabled before they can be used. Upon setting the power enable bit, the peripheral will start in default state and needs to be configured.

- When going to deep sleep, any of these peripherals that is not active should be powered down to minimize deep sleep current.

- The AmbiqSuite HAL includes power\_control functions that automate this process by saving the config setting before powering down the peripheral and write the saved settings to the peripheral when powering it back on.

#### Power Optimization: Tips

- To enable the MCU core to be put to sleep while peripherals are active, most Apollo3 peripherals have FIFOs, and many also have DMA and command queue support.

- Peripherals with FIFOs:

- IOM I2C/SPI Master: 32Bytes TX and 32Bytes RX

- MSPI: 16-entery FIFO (32 Bits Wide)

- IOS I2C/SPI Slave: 256 Byte LRAM (Direct access / FIFO)

- BLE: Virtual FIFO in BLE subsystem SRAM (42K total RAM)

- ADC: 16-deep FIFO

- PDM: 32 Words

- Peripherals with DMA support:

- IOM I2C/SPI Master, MSPI, ADC, BLE, PDM

- Peripherals with Command Queue support:

- IOM I2C/SPI Master, MSPI

#### **Default Active State**

- MCU core active with 48MHz core clock

- All Flash and RAM start powered/enabled, but cache starts disabled

- All Pins start with GPIO buffers disabled (High-Z) except for the two SWD pins and the SWO pin (GPIO41)

- GPIO20 and GPIO21 are configured as SWDIO and SWDCK with no internal pull-up/down (i.e. floating) so these either need external pull-up/down as recommended in design guide or need to be reconfigured by software. All other pins can be left unconnected.

- Note: all GPIO pins have ESD diodes that connect the GPIO pin to MCU VDD. Regardless of GPIO configuration, voltage applied to GPIO pin should not exceed VDD.

- XT and RTC clock start enabled at initial power-up. However, the standard bsp init code in the SDK stops both.

- Unlike nearly all other registers, the state of XT and RTC are not cleared by any reset other than power-on reset (to allow RTC to operate through brownout or software resets without losing time). Therefore, it is prudent to explicitly initialize these to desired state after reset regardless of default power-on-reset state. (Low power init function disables XT and RTC)

- Peripherals (I2C/SPI, MSPI, UART, ADC, PDM) start powered-off (power-gated)

#### Normal Sleep

- When normal sleep mode is entered:

- Clock is gated from the CPU Core

- Flash remains powered in standby mode

- Shutting down the upper block of Flash will reduce normal sleep power consumption)

- Everything else that was active before the sleep command remains active. HFRC continues to run but is gated from the core.

# Deep Sleep

- When Deep sleep is entered, anything that is not being used will be powered down:

- All GPIO retain state, and any GPIO can be configured to generate an interrupt which will wake the MCU from deep sleep

- Flash is shut down (so Flash power-down commands do not impact deep sleep power consumption)

- SRAM transitions to a low-power retention state

- Deep Sleep retention setting determines how much of the SRAM is retained.

- If cache is enabled, it is retained or not based on cache deep sleep retention configuration

- Any clocks (HFRC, XT, and LFRC) not being used by peripherals or timers will be stopped. Conversely, any clock that is being used will continue running.

- Any peripheral that is powered on will stay on. For lowest power deep sleep, this is the most critical item, to power down as many peripherals as possible.

- Note: this does not include RTC, CTimers, or STimer which are very low power as long as they are using LFRC, XT, or low frequency external timer input as clock sources. These can be left running in deep sleep. The XT and LFRC clocks are very low power.

# Example Power Consumption @ 3.3V

- Apollo3 does not support reducing the CPU clock, so optimal power consumption is achieved by going to sleep whenever there is no active processing.

- Example application that wakes from Deep Sleep every 10ms to perform 100µs of processing @ 48MHz:

- 2.7µA Deep Sleep

- 2.9µA Transition current for waking up 100 times/second from Deep Sleep

- Includes MCU wake-up energy consumption and active power consumption jumping to/from ISR

- 5.8µA Active Processing

- **11.4µA** Total

- Best competing processors will consume >30μA just for the active processing and most are much higher

# Example Power Consumption @ 1.8V

- Apollo3 does not support reducing the CPU clock, so optimal power consumption is achieved by going to sleep whenever there is no active processing.

- Example application that wakes from Deep Sleep every 10ms to perform 100µs of processing @ 48MHz:

- 3.8µA Deep Sleep

- 3.6µA Transition current for waking up 100 times/second from Deep Sleep

- Includes MCU wake-up energy consumption and active power consumption jumping to/from ISR

- 8.9µA Active Processing

- 16.4µA Total

- Best competing processors will consume >30μA just for the active processing and most are much higher

endpoint intelligence

# **Apollo3 Blue** Technical Details

# Apollo 3 Blue System Block Diagram

|                 |                       | MCU                    |                 |                             |          |                           | Memory                       |        | . 8                         | BTLE                          |                                 | ensor<br>ipherals                   |

|-----------------|-----------------------|------------------------|-----------------|-----------------------------|----------|---------------------------|------------------------------|--------|-----------------------------|-------------------------------|---------------------------------|-------------------------------------|

| Co              | rtex M4               | with FPU,              | Up to 96        | ARI<br>6MHz                 | <b>1</b> | 1                         | MB Flash<br>B Flash OT       | Ρ      |                             | STLE 5<br>ontroller           | 14b                             | , 1.2MS/s,<br>-Channel<br>ADC       |

| 16kB            | Wake-U                | p Pe                   | ower            | Reset                       |          | 38                        | 34kB RAM                     |        | S                           | ecurity                       |                                 | v Leakage<br>mparator               |

| Flash<br>Cache  | Interrup<br>Controlle |                        | agement<br>Jnit | Controll                    |          |                           | DMA                          | n<br>N | BT                          | LE Radio                      | Ter                             | np Sensor                           |

| Т               | iming                 |                        |                 | pper<br>otor                |          |                           | ltage<br>itoring             |        |                             |                               | erial<br>unicati                | on                                  |

| Sys Time<br>RTC | r / T                 | ïmers /<br>PWM<br>(x8) | Cont            | ammable<br>trollers<br>(x8) |          | Power-<br>On Reset        | Buck<br>Converters           |        | 50-<br>Channel<br>GPIO      | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) | Slave<br>(x1)                       |

| LFRC            | HFRC                  | XTAL                   | Ра              | mplex<br>ttern<br>erators   |          | Brown-<br>Out<br>Detector | Supply<br>Voltage<br>Monitor |        | I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

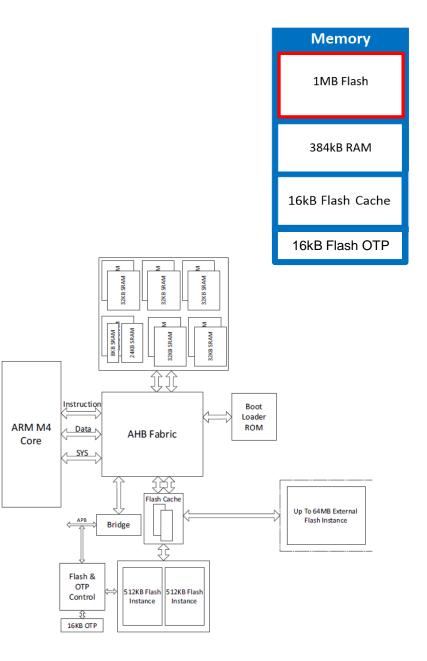

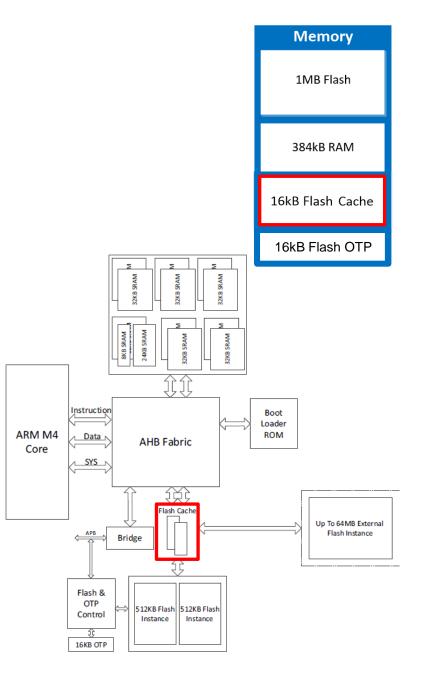

# Memory: Flash

- IMB of Flash

- 2x 512KB Flash Instances

- Independent power control

- Independent mass erase

- Flash Protection in 16KB Chunks

- Flash erase by 8KB Page

## Memory: Cache

- 16KB Cache

- 2-way set-associative or Direct Mapped

- 512/1024 entry, 128b line size

- Unified ICode and DCode cache controller Configurable to cache Instruction, Data, or Both

- Caching is supported for the entire 1MB internal Flash and the 64MB external Flash aperture (via MSPI)

- Intended to provide single cycle read access to Flash and reduce overall accesses to the Flash to reduce power.

- Two regions can be designated as noncacheable

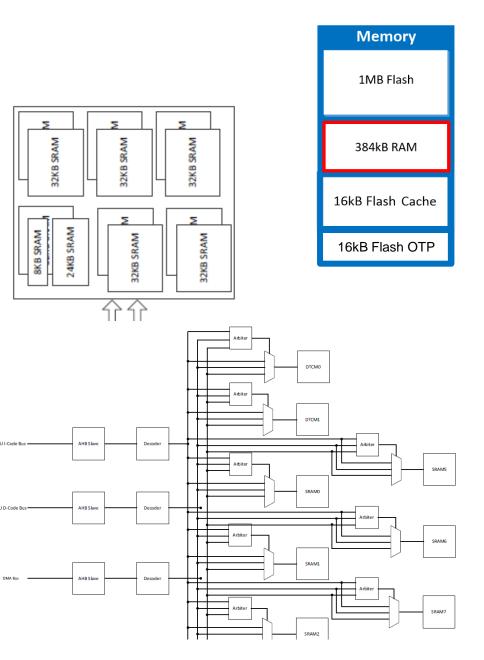

#### Memory: SRAM

- 384KB SRAM

- DTCM Banks (first 64KB) guaranteed zero waitstate unless there is contention for that specific memory array with another requestor (CPU I/D Bus or DMA Bus).

- Main SRAM banks (64K-384KB range) are zero wait-state for sequential accesses or 1-wait state for non-sequential accesses for I/D Bus accesses unless there is contention for that specific memory array

- DMA accesses to Main SRAM are always 0-wait state unless there is contention for that specific memory array

- Prefetching is used on the I/D Bus accesses to Main SRAM to minimize/eliminate wait-state bubbles. Prefetching can be enabled/disabled for I and/or D Bus accesses

- Arbitration logic for each SRAM instance allows one bus slave access to the SRAM on any given cycle.

# Memory: Flash OTP – INFO Space

- 16KB of Secure Flash "OTP"

- 8 KBytes contain factory preset chip trim values.

- 8 KBytes for customer use:

- Security

- Secure Bootloader Configuration

- **Flash Protection**

- Debug Lockout

- Customer Options/Trims

- **Enable SIMO-Buck**

- Enable BLE

- Enable BLE Buck

- 32MHz XTAL Trim

Core

16KB OT P

# Memory: Flash OTP – INFO Space

- Apollo3 EVBs ship with pre-configured customer INFO0 with these settings:

- SIMO-Buck, BLE, and BLE Buck enabled

- Secure Bootloader (SBL) set for non-secure mode

- SBL configured to use UART at 115Kbaud and TX=GPIO22, RX=GPIO23 (which are connected to onboard USB-to-UART)

- Apollo3 parts ship with non-initialized customer INFO0

- SIMO-Buck, BLE, and BLE Buck are disabled

- SBL defaults to UART at 115Kbaud using GPIO

|   | Memory           |

|---|------------------|

|   | 1MB Flash        |

| ) | 384kB RAM        |

|   | 16kB Flash Cache |

|   | 16kB Flash OTP   |

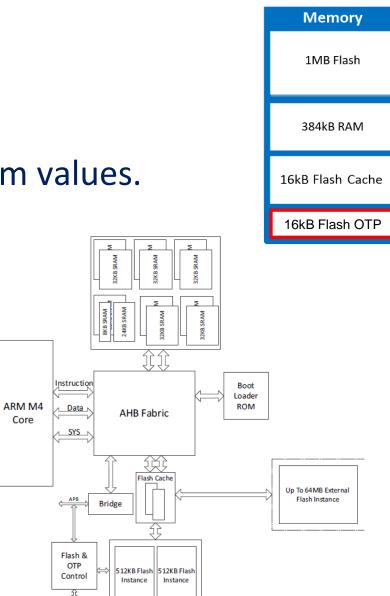

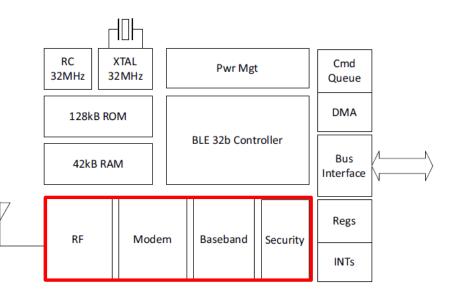

# **Timing: Clock Generation**

- Multiple clock sources available for peripherals

- All 3 sources can be divided down in most cases

- 32.768 kHz XTAL is most accurate, but requires crystal

- HFRC (High Freq. RC oscillator)

- 48MHz or 96MHz

- Consumes most power

- 2% accurate at 25C across voltage (1.8V to 3.6V)

- TBD accuracy across -40C to 85C

- Autoadjust function continuously calibrates HFRC to XTAL to ensure < 1% error (<0.1% error at stable temp)</li>

- LFRC (Low Freq. RC oscillator)

- Nominally 1.024 kHz

- Low power but inaccurate (25%+ error)

- Core and Flash only clocked via HFRC at 48MHz or 96MHz

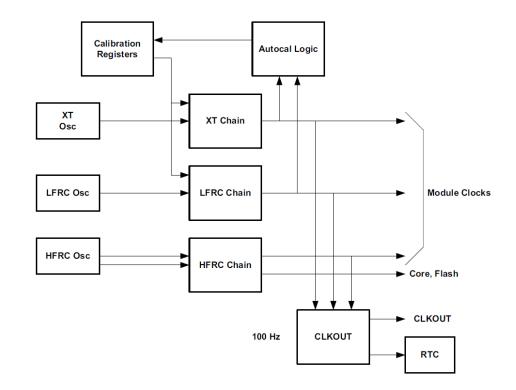

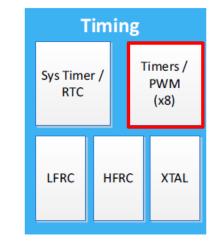

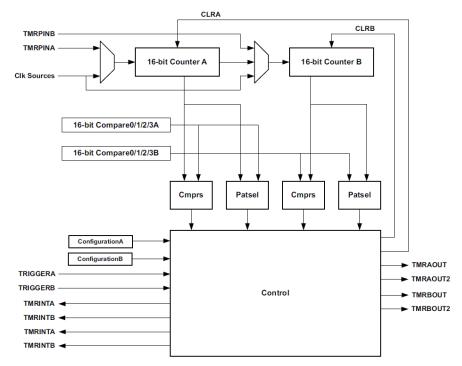

# Timing: Counter/Timers - Ctimers

- Supports multiple clock sources

- As fast as 12MHz (HFRC/4)

- As slow as 1Hz (LFRC/1024)

- 8 total Ctimer Pairs

- Up to 16, 16-bit timers

- Up to 8, 32-bit timers

- 4 compare modules per Ctimer

- Standard Counter functionality:

- Interrupt after a specified delay

- Interrupt periodically with a specified period

- Generate an external pulse of a specified width, after a configured delay

- Generate an external PWM signal with a specified period and duty cycle

# Timing: Counter/Timers - Ctimers

- Advanced Ctimer Features:

- Arbitrary pattern generation

- Up to 128-bits in HW register

- Longer continuous pattern supported by updating when half of pattern register has been output (i.e. interrupt generated every 64-bits for MCU to service)

- Timer-synchronization features so pattern outputs from multiple timers can be perfectly aligned

- Applications include stepper motor control, streaming serial data such as PDM audio output, etc.

- Alternating PWM pulse output (can be used as double-buffered PWM)

- Improved PWM "DAC" output for LED dimming, PWM audio output, etc.

- Timers can select the output of other Ctimers as their clock source (in addition to LFRC, XT, and HFRC derived clock sources)

# Timing: Real Time Clock (RTC) Module

- Same RTC IP as AMx8x5 devices

- Clocked from XTAL or LFRC

- 100<sup>th</sup> of a second resolution (10ms)

- Automatic leap year calculation

- Programmable alarm interrupts

- Every 100th sec., 10th sec., sec., min., hour, day, week, month, or year

- Continues to operate through all resets except POA power-on reset which occurs at TBD voltage (~1.3V) so time is retained through all other resets including brownout

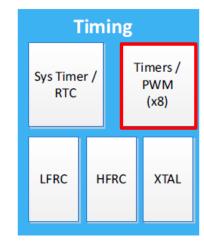

# Timing: System Timer (Stimer) Module

- 32bit System Timer

- Clocked from XTAL, LFRC, or HFRC/16

- 8x 32bit compare registers with interrupts

- Offsets from "NOW" are written to compare registers and compare register value is determined by HW

- Only reset by POA (Power On Analog system cold reset). Retains time across all POI and POR (system warm reset) events except full power cycle.

- Contains three 32-bit NVRAM registers that are only reset by POA

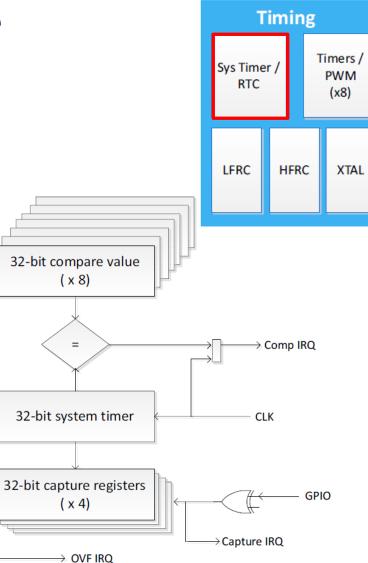

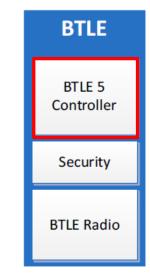

# Bluetooth Low Energy BLE 5

- Bluetooth 5 Compliant (QDID: 115953)

- Secure connection (AES-128 HW Encryption)

- Extended packet length support

- Up to eight simultaneous connections

- -93 dBm sensitivity

- -20 to +4 dBm TX output power range

- Power amplifier controls enable higher TX power with external PA

- Single ended output

- Integrated Balun and antenna matching network

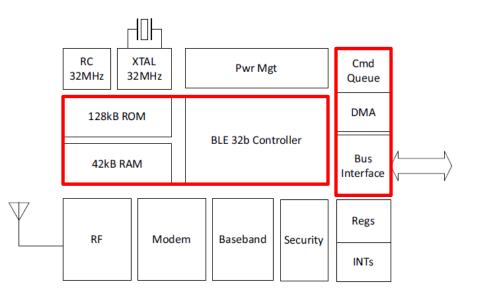

# **Bluetooth Low Energy BLE 5**

- Dedicated 32bit processor for BLE Controller

- 128K ROM and 42K RAM

- BLE Controller Stack runs on BTLE controller

- HCI interface to main processor.

- HCI interface has FIFO, DMA, and command queue to minimize interruption of host processor

- Cordio-B50 BLE 5 Compliant Host Stack (QDID: 91368) runs on main CM4 processor

- Basic application including FreeRTOS, BLE Host Stack, plus basic BLE profile such as HRM requires approximately 80K Flash and 35K SRAM

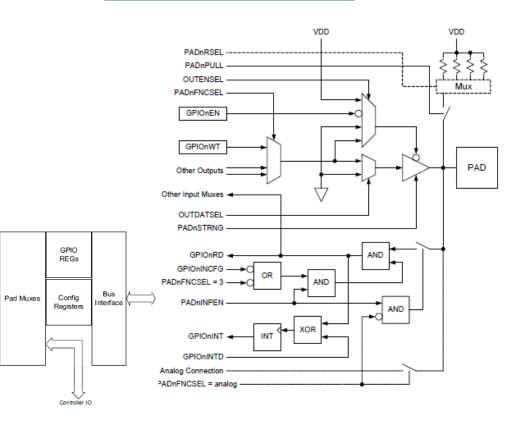

# Serial Communication: GPIO

- 50 GPIO on BGA, 37 GPIO on CSP

- Configurable

- Tristate, Open Drain, or Push Pull

- Configurable drive strength or 2, 4, 8, or 12mA

- Many pin function mapping options

- Integrated pull up/down

- 3 power GPIOs (2 source, 1 sink)

- Each can support up to a 50mA continuous load

|                             | С | S<br>omm                      | erial<br>unica          | atic | on | 1                                   |  |

|-----------------------------|---|-------------------------------|-------------------------|------|----|-------------------------------------|--|

| 50-<br>Channel<br>GPIO      |   | UART<br>(x2)                  | PD<br>Ma:<br>(x<br>ster | (1   |    | I2S<br>Slave<br>(x1)                |  |

| I2C / SPI<br>Master<br>(x6) |   | I2C /<br>SPI<br>Slave<br>(x1) | ISO78<br>Mast<br>(x1    | ter  | c  | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |  |

# Serial Communication: GPIO

• Flexible Pin-Function mapping:

| Pad      | 0                                       | 1<br>T             | Pad Function 2 |                  | Number (PA                            |                   | .)<br>6           | 7        | CSP<br>PKG   | Max<br>Drive<br>Streng | NCE Chp Select Mux                           |   | CT C<br>Ing<br>Select | at       | 2        |        | I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1) | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

|----------|-----------------------------------------|--------------------|----------------|------------------|---------------------------------------|-------------------|-------------------|----------|--------------|------------------------|----------------------------------------------|---|-----------------------|----------|----------|--------|-----------------------------|-------------------------------|---------------------------|-------------------------------------|

| 0        | SLSCL                                   | SLSCK              | CLKOUT         | GPI000           |                                       | MSPI4             |                   | NCEO     | x            | 12mA                   | M3.2 M4.2 M5.2 M1.3                          | - |                       |          |          | -      |                             |                               |                           |                                     |

| 1        | SUSDAWIRS                               | SLMOSI             | UARTOTX        | GPI001           |                                       | MSPI5//           |                   | NCE1     | x            | 12mA                   | M0.2 M1.2 M2.2 MSPI.0                        |   |                       |          |          | _      |                             |                               |                           |                                     |

| 2        | UART1RX                                 | SLMISO             | UARTORX        | GP1002           |                                       | MSPI6             | -                 | NCE2     | x            | 12mA                   | M3.3 M4.3 M5.3 M2.1                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 3        | UAORTS                                  | SLICE              | /////          | GPI003"          |                                       | MSP17             | TRIG1             | 128_WOLK | х            | 12mA                   | M3.0 M4.0 M5.0 M2.0                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 4        | UA0CTS                                  | SLINT              | NCE4           | GPIO04           | •                                     | UART1RX           | CT17              | MSPI2    | х            | 12mA                   | M3.1 M4.1 M5.1 M1.1                          |   |                       | A4       | A4OUT2 E | 37001  | A4OUT A                     | OUT2 A6OUT2                   | 2 A7OUT2                  |                                     |

| 5        | MOSCL                                   | MOSCK              | UAORTS         | GPI005           | · · · · · · · · · · · · · · · · · · · |                   |                   | СТ8      | x            | 12mA                   |                                              |   | A2                    |          |          |        |                             | SOUT A6OUT2                   |                           |                                     |

| 6        | MOSDAWIRS                               | MOMISO             | UAOCTS         | GPI006           | · · · · · · · · · · · · · · · · · · · | CT10              | •                 | I2S_DAT  | х            | 12mA                   |                                              |   | B2                    |          |          |        |                             | SOUT A6OUT2                   |                           |                                     |

| 7        | /////////////////////////////////////// | MOMOSI             | 214,515        | GPI007           | TRIGO                                 | UARTOTX           |                   | CT13     | x            | 12mA                   | M3.1 M4.1 M5.1 MSPL0                         |   |                       | B4       | B4OUT2 # | 12001  | F B4OUT B                   | OUT2 A6OUT2                   | 2 A7OUT2                  |                                     |

| 8        | MISCL                                   | MISCK              | NCE8           | GPI008           | SCCCLK                                | •                 | UARTITX           | •        | x            | 12mA                   | M3.0 M4.0 M5.0 M0.0                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 9        | MISDAWIR                                | MIMISO             | NCE9           | GPI003           | SCCIO                                 | •                 | UART1RX           | •        | x            | 12mA                   | M3.3 M4.3 M5.3 M2.3                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 10<br>11 | UARTITX<br>ADCSE2                       | MIMOSI             | NCE10<br>CT31  | GPIO10           | PDM_CLK<br>SLINT                      | UAIRTS            | -                 | -        | X<br>X       | 12mA                   | M3.2 M4.2 M5.2 MSPI.0<br>M0.0 M1.0 M2.0 M3.0 |   |                       | B7       | DZOLITO  | 000    |                             |                               | A70UT0                    |                                     |

| 11       | ADCD0NSE9                               | 540512             | CT 31          | GPI011<br>GPI012 | SLINI                                 | UAICTS<br>PDM_CLK | UARTORX<br>UA0CTS |          | x            | 12mA<br>12mA           | M3.0 M4.0 M5.0 MSPI.1                        |   | A0                    | ВГ       |          |        |                             | OUT2 A6OUT2<br>SOUT A6OUT2    |                           |                                     |

| 13       | ADCD0PSE8                               | NCE13              | CT2            | GPI012           | I2S_BCLK                              | POWLCER           | UAORTS            | UARTIRX  | <del>x</del> | 12mA                   | M3.1 M4.1 M5.1 M0.1                          |   | B0                    |          |          |        |                             | 7OUT A6OUT2                   |                           |                                     |

| 14       | ADCD1P                                  | NCE14              | UARTITX        | GPI014           | PDM_CLK                               |                   | SWDCK             | 32KHz_XT | x            | 12mA                   | M0.2 M1.2 M2.2 M4.2                          |   | - 00                  |          | 00001 1  | 1001.  | 2 000012 M                  | 1001 A00012                   | . 410012                  |                                     |

| 15       | ADCD1N                                  | NCE15              | UART1RX        | GPIO15           | PDM_DATA                              |                   |                   | SWO      | x            | 12mA                   | M0.3 M1.3 M2.3 MSPI.0                        |   |                       |          |          |        |                             |                               |                           |                                     |

| 16       | ADCSE0                                  | NCE16              | TRIGO          | GPIO16           | SCCRST                                | CMPIN0            | UARTOTX           | UAIRTS   | x            | 12mA                   | M0.0 M1.0 M2.0 M5.0                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 17       | CMPRF1                                  | NCE17              | TRIGI          | GPI017           | SCCCLK                                |                   | UARTORX           | UAICTS   | x            | 12mA                   | M0.1 M1.1 M2.1 M4.1                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 18       | CMPIN1                                  | NCE18              | CT4            | GPIO18           | UAORTS                                |                   | UARTITX           | sceio    | x            | 12mA                   | M0.2 M1.2 M2.2 M3.2                          |   | A1                    |          | A10UT A  | 20UT   | 2 ASOUT2 B                  | SOUT A6OUT2                   | A7OUT2                    |                                     |

| 19       | CMPRF0                                  | NCE19              | CT6            | GPI019           | SCCCLK                                |                   | UART1RX           | I2S_BCLK | х            | 12mA                   | M0.3 M1.3 M3.3 MSPL0                         |   | B1                    |          | B1OUT    | 410UT  | B50UT2 B                    | 70UT A60UT2                   | 2 A7OUT2                  |                                     |

| 20       | SWDCK                                   | NCE20              |                | GPI020           | UARTOTX                               | UARTITX           | I2S_BOLK          | UAIRTS   | х            | 4mA                    | M3.1 M4.1 M5.1 M2.1                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 21       | SWDIO                                   | ///%%%%%////       |                | GPI021           | UARTORX                               | UART1RX           | SCORST            | UAICTS   | x            | 12mA                   | M3.2 M4.2 M5.2 M2.2                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 22       | UARTOTX                                 | NCE22              | CT12           | GPI022           | PDM_CLK                               |                   | MSPI0             | SWO      | x            | 12mA                   | M3.3 M4.3 M5.3 M0.3                          |   | A3                    |          |          | 310UT  |                             | OUT2 A6OUT2                   |                           |                                     |

| 23       | UARTORX                                 | NCE23              | CT14           | GPIO23           | I2S_WOLK                              | CMPOUT            | MSPI3             |          | x            | 12mA                   | M0.0 M1.0 M2.0 M4.0                          |   | B3                    | 15       |          | 310UT  |                             | 70UT A60UT2                   |                           |                                     |

| 24<br>25 | UARTITX<br>UARTIRX                      | NCE24<br>NCE25     | MSPI8<br>CT1   | GPIO24           | UA0CTS<br>M2SDAWIR3                   | CT21<br>M2MISO    | 32KHz_XT          | swo      | X            | 12mA                   | M0.1 M1.1 M2.1 M5.1<br>M3.2 M4.2 M5.2 M0.2   |   |                       | A5<br>A0 |          |        |                             | OUT2 A6OUT2                   |                           |                                     |

| 25       | UARTIRA                                 | NCE25              | СТЗ            | GPI025<br>GPI026 | SCCRST                                | MSPI1             | UARTOTX           | UA1CTS   | X<br>X       | 12mA<br>12mA           | M3.3 M4.3 M5.3 M1.3                          |   |                       | B0       |          |        |                             | OUT2 A6OUT2<br>SOUT A6OUT2    |                           |                                     |

| 20       | UARTORX                                 | NCE20              | CTS            | GPIO20           | M2SCL                                 | M2SCK             |                   |          | Î            | 12mA                   | M3.0 M4.0 M5.0 M1.0                          |   |                       | A1       |          |        |                             | 70UT A60UT2                   |                           |                                     |

| 28       | I2S_WCLK                                | NCE28              | СТ7            | GPI028           |                                       | M2MOSI            | UARTOTX           |          | x            | 12mA                   | M3.1 M4.1 M5.1 MSPL0                         |   |                       | B1       |          |        |                             | 70UT A60UT2                   |                           |                                     |

| 29       | ADCSE1                                  | NCE29              | стэ            | GPI023           | UA0CTS                                | UAICTS            | UARTORX           | PDM_DATA | x            | 12mA                   | M3.2 M4.2 M5.2 M1.2                          |   |                       | A2       |          |        |                             | DOUT AGOUT2                   |                           |                                     |

| 30       |                                         | NCE30              | CT11           | GPI030           | UARTOTX                               | UAIRTS            |                   | I2S_DAT  |              | 12mA                   | M3.3 M4.3 M5.3 M0.3                          |   |                       | B2       |          |        |                             | OUT2 AGOUT2                   |                           |                                     |

| 31       | ADCSE3                                  | NCE31              | CT13           | GPI031           | UARTORX                               | SCCCLK            |                   | UAIRTS   |              | 12mA                   | M0.0 M1.0 M2.0 M4.0                          |   |                       | A3       |          |        |                             | OUT2 A6OUT2                   |                           |                                     |

| 32       | ADCSE4                                  | NCE32              | CT15           | GPI032           | SCCIO                                 |                   |                   | UAICTS   |              | 12mA                   | M0.1 M1.1 M2.1 MSPI.1                        |   |                       | B3       | B3OUT2 E | 33001  | A7OUT A4                    | OUT2 A6OUT2                   | A7OUT2                    |                                     |

| 33       | ADCSE5                                  | NCE33              | 32KHz_XT       | GPI033           |                                       | UA0CTS            | CT23              | SWO      |              | 12mA                   | M0.2 M1.2 M2.2 M5.2                          |   |                       | B5       | BSOUT2 / | 17001  | ASOUT BO                    | IOUT2 A6OUT2                  | 2 A7OUT2                  |                                     |

| 34       | ADCSE6                                  | NCE34              | UAIRTS         | GPIO34           | CMPRF2                                | UAORTS            | UARTORX           | PDM_DATA |              | 12mA                   | M0.3 M1.3 M2.3 M3.3                          |   |                       |          |          |        |                             |                               |                           |                                     |

| 35       | ADCSE7                                  | NCE35              | UARTITX        | GPI035           | I2S_DAT                               | CT27              | UAORTS            |          |              | 12mA                   | M0.0 M1.0 M2.0 M3.0                          |   |                       | B6       | B6OUT2   | A1OUT  | B6OUT B2                    | OUT2 A6OUT2                   | 2 A7OUT2                  |                                     |

| 36       | TRIGI                                   | NCE36              | UART1RX        | GPIO36"          | 32KHz_XT                              | UAICTS            | UA0CTS            | PDM_DATA |              | 12mA                   | M3.1 M4.1 M5.1 MSPL1                         |   |                       |          |          |        |                             |                               |                           |                                     |

| 37       | TRIG2                                   | NCE37              | UAORTS         | GPI037**         | SCCIO                                 | UARTITX           | PDM_CLK           | СТ29     |              | 12mA                   | M3.2 M4.2 M5.2 M0.2                          |   |                       | A7       | BSOUT2   | 410UT  | A7OUT A3                    | OUT2 A6OUT2                   | A/OUT2                    |                                     |

| 38       | TRIG3                                   | NCE38              | UAOCTS         | GPI038           |                                       | M3MOSI            | UART1RX           | •        |              | 12mA                   | M0.3 M1.3 M2.3 M5.3                          |   |                       | 40       |          | 2001/2 |                             |                               | A70UT0                    |                                     |

| 39<br>40 | UARTOTX<br>UARTORX                      | UARTITX<br>UARTIRX | CT25<br>TRIG0  | GPIO39<br>GPIO40 | M4SCL<br>M4SDAWIR3                    | M4SCK<br>M4MISO   | :                 |          | x            | 12mA<br>12mA           |                                              |   |                       | A6       | 840012   | 52001  | ABOUT A2                    | OUT2 A6OUT2                   | A70012                    |                                     |

| 40       | NCE41                                   | OARTIKA            | SWO            | GPIO40           | I2S_WCLK                              | UAIRTS            | UARTOTX           | UAORTS   | X            | 12mA<br>12mA           | M0.1 M1.1 M2.1 MSPL1                         |   | ———                   |          |          |        |                             |                               |                           |                                     |

| 41       | UARTITX                                 | NCE42              | CT16           | GPI041<br>GPI042 | M3SCL                                 | M3SCK             |                   |          | <u> </u>     | 12mA                   | M0.0 M1.0 M2.0 M5.0                          |   | A4                    |          |          | ייורות |                             |                               |                           |                                     |

| 43       | UARTIRX                                 | NCE42              | CT18           | GPIO43           | M3SDAWIR3                             | M3MISO            |                   |          |              | 12mA                   | M0.1 M1.1 M2.1 MSPI.1                        |   | B4                    |          |          |        |                             | OUT2 A6OUT2                   |                           |                                     |

Serial

Communication

UART

(x2)

50-

Channel

GPIO

PDM

Master

(x1

stereo)

12S

Slave

(x1)

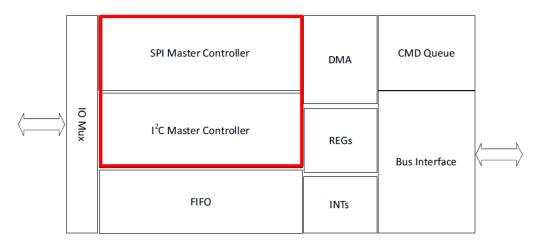

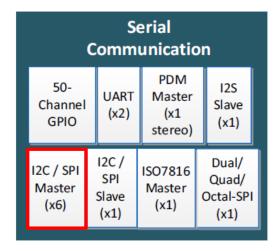

# Serial Communication: I/O Masters (IOM)

- 6 total IOMs (I/O Masters) available

- Each can be configured for SPI or I2C

- I2C mode

- Supports 7 and 10-bit addressing

- Multi-master arbitration

- 100KHz, 400KHz, and 1MHz

- Integrated pull-up resistors

- SPI mode

- 8 Chip Selects per IOM

- 3 and 4-wire modes

- Up to 24 MHz

- Supports all 4 standard SPI modes

- Standard embedded address (command byte) operations

- Also supports raw read/write operations

|                             |                               | erial<br>unicatio               | on                                  |

|-----------------------------|-------------------------------|---------------------------------|-------------------------------------|

| 50-<br>Channel<br>GPIO      | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) | I2S<br>Slave<br>(x1)                |

| I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

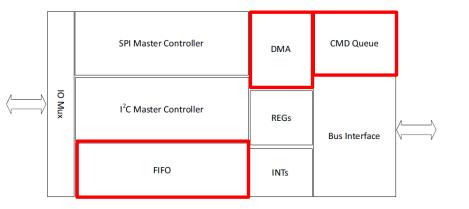

# Serial Communication: I/O Masters

- Each IOM contains independent Read and Write FIFOs of 32Bytes

- Each IOM has a DMA controller that supports IOM to SRAM, and SRAM/Flash to IOM transfers

- Each IOM supports command queues which can schedule multiple transactions to occur without CPU intervention.

- Used in combination with DMA.

- CPU can go to sleep while IOM is performing direct reads/writes to/from FIFO or transferring data by way of DMA

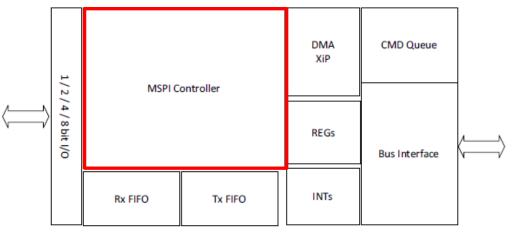

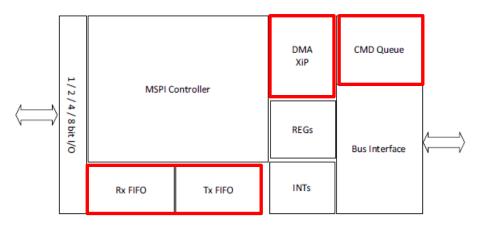

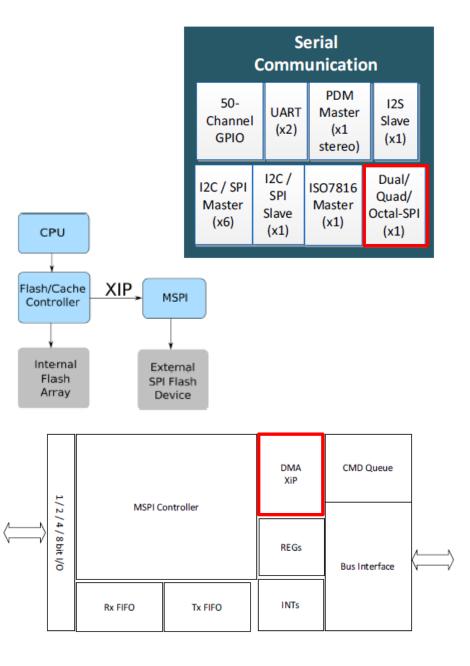

# Serial Communication: MSPI

- One MSPI Master Module

- Supports Serial, Dual, Quad, and Octal modes

- 2 Chip Selects

- Up to 24 MHz Clock

- Supports all 4 standard SPI modes

|                             |                               | erial<br>unicatio               | on                                  |

|-----------------------------|-------------------------------|---------------------------------|-------------------------------------|

| 50-<br>Channel<br>GPIO      | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) | I2S<br>Slave<br>(x1)                |

| I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

# Serial Communication: MSPI

- Unified 16-entry FIFO (32 bits wide) for reads and writes

- DMA Support

- Simple DMA model where software sets internal (SRAM or flash) address and external device address, transfer direction, and transfer size

- MSPI DMA controller automatically handles sequencing of instructions and address to serial flash device.

- Software configures registers to specify device read/write command bytes and address bytes (1 to 4).

- Command Queue

- Software can construct a buffer of operations and MSPI w execute the series of operations autonomously

- Used in combination with DMA

|                             | С | S<br>omm                      | erial<br>unica            | ntio     | n                                   |  |  |  |

|-----------------------------|---|-------------------------------|---------------------------|----------|-------------------------------------|--|--|--|

| 50-<br>Channel<br>GPIO      |   | UART<br>(x2)                  | PD<br>Mas<br>(x:<br>stere | ter<br>1 | I2S<br>Slave<br>(x1)                |  |  |  |

| I2C / SPI<br>Master<br>(x6) |   | I2C /<br>SPI<br>Slave<br>(x1) | ISO78<br>Maste<br>(x1)    | er       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |  |  |  |

#### Table 363: FLASH Register

| 3 | 3 | 2  | 2   | 2   | 2  | 2 | 2 | 2 | 2 | 2  | 2    | 1   | 1  | 1 | 1 | 1 | 1 | 1   | 1 | 1 | 1 | 0        | 0 | 0        | 0        | 0         | 0            | 0      | 0 | 0    | 0     |

|---|---|----|-----|-----|----|---|---|---|---|----|------|-----|----|---|---|---|---|-----|---|---|---|----------|---|----------|----------|-----------|--------------|--------|---|------|-------|

| 1 | 0 | 9  | 8   | 7   | 6  | 5 | 4 | 3 | 2 | 1  | 0    | 9   | 8  | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | 9        | 8 | 7        | 6        | 5         | 4            | 3      | 2 | 1    | 0     |

|   |   | RE | EAD | INS | TR |   |   |   |   | WF | RITE | INS | TR |   |   |   | F | svi | D |   |   | XIPMIXED |   | XIPSENDI | XIPSENDA | XIPENTURN | XIPBIGENDIAN | XIPACK |   | RSVD | XIPEN |

# Serial Communication: MSPI

- MSPI supports Execute in Place (XIP) Operations

- MSPI connected devices can be mapped into flash cache's address space and appear as extension to the internal flash. The flash/cache module will decode the address region and forward operations to the MSPI interface for completion.

- XIP and DMA/PIO operations can be interleaved.

MSPI controller will allow current operation to complete before performing the XIP operation.

- Exception: XIP mode may have to be disabled during flash programming operations.

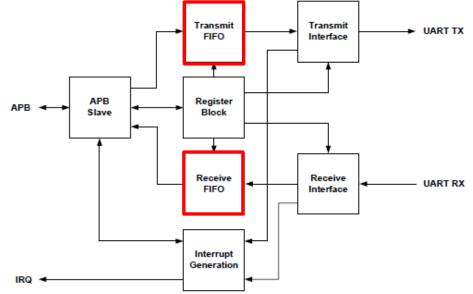

# Serial Communication: UART

- 2 UARTs

- MCU can enter **sleep mode** during transfers

- 32Byte Transmit and 32Byte receive FIFOs reduce MCU active time

- Configurable baud rate generator

- Maximum rate of 921,600 bps

- Highly programmable

- Data size, parity, and stop bit length

- Hardware flow control

- Full-duplex and half-duplex modes

- Loopback functionality for diagnostics and testing

|                             | С |                               | erial<br>unicatio               | DI | n                                   |

|-----------------------------|---|-------------------------------|---------------------------------|----|-------------------------------------|

| 50-<br>Channel<br>GPIO      |   | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) |    | I2S<br>Slave<br>(x1)                |

| I2C / SPI<br>Master<br>(x6) |   | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | (  | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

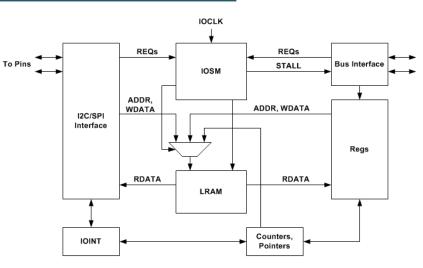

### Serial Communication: I/O Slave

- 1 IOS (I/O Slave)

- I2C or SPI mode

- I2C mode:

- configurable 7 and 10-bit addressing

- interface freq. up to 1.2 MHz

- SPI mode:

- Supports all polarity/phase combinations

- interface freq. up to TBD MHz

|                             |                               | erial<br>unicatio               | on                                  |

|-----------------------------|-------------------------------|---------------------------------|-------------------------------------|

| 50-<br>Channel<br>GPIO      | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) | I2S<br>Slave<br>(x1)                |

| I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

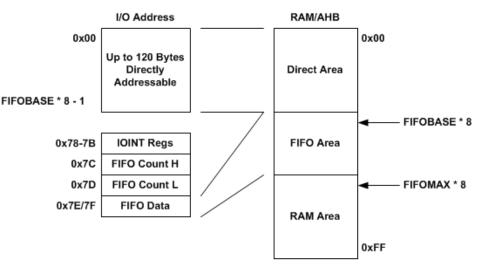

### Serial Communication: I/O Slave

- IOS LRAM is 256 bytes

- Broken up into 3 sections:

- 1. Directly addressable RAM up to 120 Bytes which can be accessed by external IOM host while MCU is asleep

- 2. Status and Config Registers & FIFO. FIFO size up to 256 Bytes

- 3. Any LRAM not configured as direct access or FIFO is left as RAM accessible by Apollo SW only

|                             | C |                               | erial<br>unicatio               | DI | n                                   |  |

|-----------------------------|---|-------------------------------|---------------------------------|----|-------------------------------------|--|

| 50-<br>Channel<br>GPIO      |   | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) |    | I2S<br>Slave<br>(x1)                |  |

| I2C / SPI<br>Master<br>(x6) |   | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | (  | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |  |

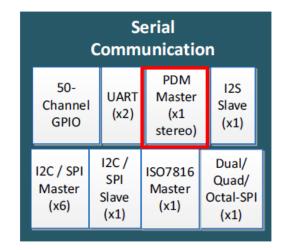

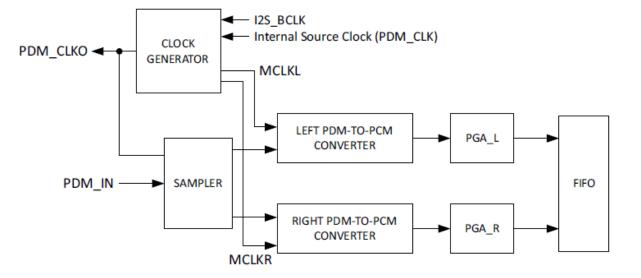

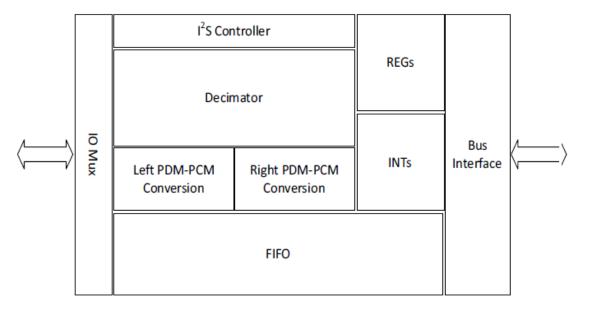

### **PDM Master Interface**

- Stereo or mono PDM input, with variable PDM output clock rates (750-768kHz, 1.5-1.536MHz, 3-3.072MHz

- Hardware performs 64x Decimation of PDM bitstream input to 16bit PCM

- 32 Sample FIFO

- DMA can efficiently transfer audio samples from FIFO to SRAM

### **I2S Slave Interface**

- I2S Slave interface is limited to direct pass-through output of audio data from PDM input (after PDM-to-PCM conversion)

- Audio data from PDM input can be simultaneously buffered in FIFO (for use by MCU) and output on I2S

- I2S does not support audio input, or output of arbitrary audio from MCU core

|                             |                               | erial<br>unicatio               | on                                  |

|-----------------------------|-------------------------------|---------------------------------|-------------------------------------|

| 50-<br>Channel<br>GPIO      | UART<br>(x2)                  | PDM<br>Master<br>(x1<br>stereo) | I2S<br>Slave<br>(x1)                |

| I2C / SPI<br>Master<br>(x6) | I2C /<br>SPI<br>Slave<br>(x1) | ISO7816<br>Master<br>(x1)       | Dual/<br>Quad/<br>Octal-SPI<br>(x1) |

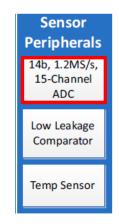

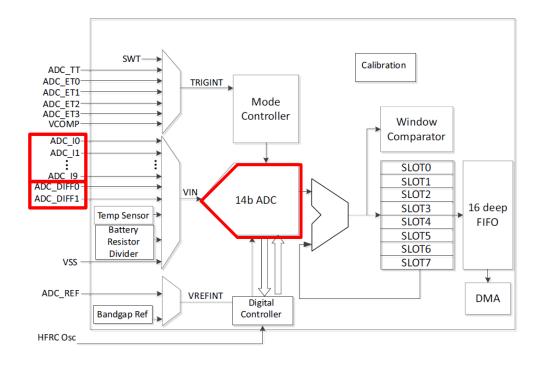

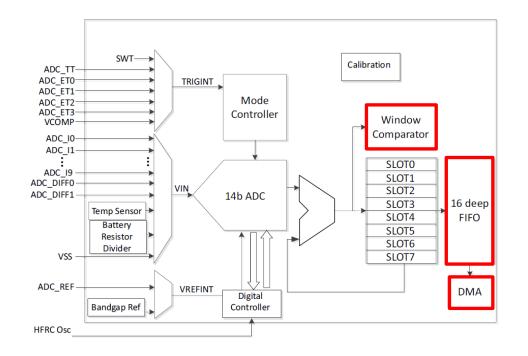

### Sensor Peripherals: ADC

- 14-bit SAR architecture (successive approximation register)

- 10 Single-ended and 2 Differential external inputs

- 3 internal inputs: VSS, Temp Sensor, and VDD/3

- On-chip bandgap or external reference voltage (2.0V or 1.5V)

- Single shot, repeating single shot, scan, and repeating scan modes

- User-selectable clock source for variable sampling rates

### Sensor Peripherals: ADC

- Multiple conversion triggers: External pins, Ctimer, SW trigger

- Window comparator for monitoring voltage excursions into or out of selectable thresholds

- 16-entry FIFO and DMA for storing measurement results and maximizing MCU sleep time

- Multiple low power modes

- Selectively shut down portions of the ADC between conversions

- Sample rate up to 1.2Msps at 14bit and up to 2.8Msps at 8bit

- Built-in accumulate and scale module

- Automatically accumulate up to 128 samples (Per-slot 21bit accumulation register)

- Scaling capability for automated averaging

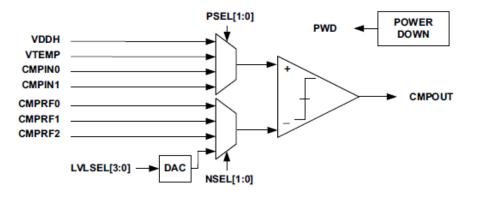

### Sensor Peripherals: Voltage Comparator

- Interrupt and register access to comparator output

- If V<sub>+</sub> rises above or falls below threshold: generates interrupt

- Programmable compare threshold:

- 4-bit DAC

- 3 different external pins

- Power consumption TBD (~2µA)

0P58V = 0x0 - Set Reference input to 0.58 Volts. 0P77V = 0x1 - Set Reference input to 0.77 Volts 0P97V = 0x2 - Set Reference input to 0.97 Volts. 1P16V = 0x3 - Set Reference input to 1.16 Volts. 1P35V = 0x4 - Set Reference input to 1.35 Volts. 1P55V = 0x5 - Set Reference input to 1.55 Volts. 1P74V = 0x6 - Set Reference input to 1.74 Volts. 1P93V = 0x7 - Set Reference input to 1.93 Volts. 2P13V = 0x8 - Set Reference input to 2.13 Volts. 2P32V = 0x9 - Set Reference input to 2.32 Volts. 2P51V = 0xA - Set Reference input to 2.51 Volts. 2P71V = 0xB - Set Reference input to 2.71 Volts. 2P90V = 0xC - Set Reference input to 2.90 Volts. 3P09V = 0xD - Set Reference input to 3.09 Volts. 3P29V = 0xE - Set Reference input to 3.29 Volts. 3P48V = 0xF - Set Reference input to 3.48 Volts.

### Sensor Peripherals: Temperature Sensor

- Built-in sensor, accessible via ADC channel or Comparator

- ± 3°C accuracy (if calibrated)

- 3.8mV/C sensor slope

- 3 calibration values needed

- Offset

- Voltage

- Temp. during calibration

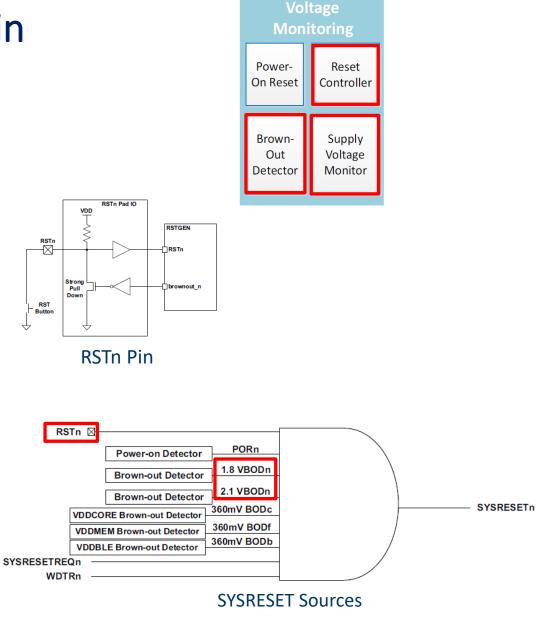

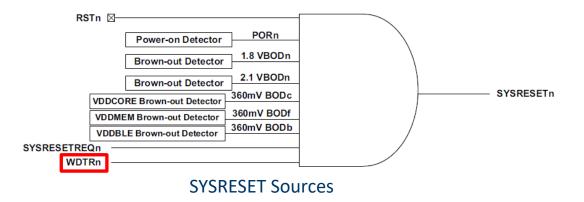

### **Reset Controller**

- Three levels of Reset

- POR = POR Software Reset = HRESET = SYSRESETn

- POI = POI Software Reset

- POA = Power-on Reset

- Most resets trigger POR reset, which is the shallowest Reset

- POI Software reset is slightly deeper reset that triggers INFO space settings to be reloaded from Flash

- POA is the deepest reset, and is only triggered by voltage going below POA voltage (~1.3V see datasheet for the exact voltage)

|                        |       |       | INEO Sottings | Dorinhorals         |                |

|------------------------|-------|-------|---------------|---------------------|----------------|

|                        |       |       | INFO Settings |                     |                |

|                        |       |       | (Trims,       | ( <u>Except</u> XT, |                |

|                        |       |       | Options, and  | LFRC, RTC, and      | XT, LFRC, RTC, |

| Reset Level            | CPU   | GPIO  | Security)     | Stimer)             | and Stimer     |

| POR (HRESET/SYSRESETn) | Reset | Reset | Not Reset     | Reset               | Not Reset      |

| POI                    | Reset | Reset | Reset         | Reset               | Not Reset      |

| Power-on Reset (POA)   | Reset | Reset | Reset         | Reset               | Reset          |

### Reset: Voltage Monitoring and nRST pin

- BOD Reset max threshold 1.755V

- Optional BODH 2.1V brownout configurable for Reset or Interrupt

- External RSTn pin has built-in weak pull-up resistor

- RSTn pin is driven low when brownout is detected

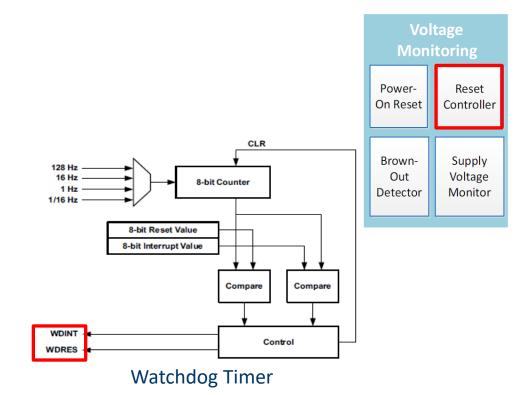

### Reset: Watchdog Timer

- WDT (watchdog timer)

- Clocked from LFRC with divider options from 1/16Hz to 128Hz

- Two configurable WDT 8-bit register compare values:

- One compare for Interrupt

- One compare for Reset

### Reset: Power on Reset (POA)

- Some registers are only reset by System Power-Down (POA) which occurs ~1.3V (see datasheet for the exact voltage)

- During all other resets, including RSTn, BOD, WDT, and POR and POI Software resets, the following are retained:

- All RTC registers retain state

- RTC and STIMER counters continue operation from 32kHz XTAL or from LFRC (if below BODL). If clock sources stop oscillating at very low voltage, the RTC and STIMER will continue to maintain state.

- Clock configuration registers retain state

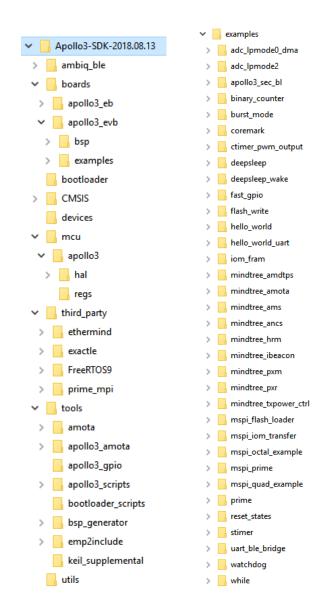

### AmbiqSuite SDK

- Register files (CMSIS compatible)

- HAL source code

- Mindtree Ethermind BLE Stack

- BSP source code for each EVB

- Extensive software examples

- Source code

- Keil, IAR, and GCC project files

- Application Notes

- API documentation

### Ambiq Suite: HAL

- HAL (hardware abstraction layer) makes using Apollo easier

- Abstraction provides simple functions and macros for enabling and using peripherals

- HAL also provides macros that make constants easier to read and use

- AM\_HAL\_ADC\_CLOCK\_12MHZ instead of 0x01000000

- Several functions based on C macros that minimize number of executed instructions

### Ambiq Suite: BSPs

- A BSP (board support package) contains additional functions and macros for use with specific board hardware

- Each EVK board has its own BSP

- BSPs make prototyping with Ambiq evaluation materials easier

- All Ambiq Suite code examples include use of BSP functions

### Ambiq Debug Tools

- Ambig Micro MCUs are supported by industry standard tools

- Standard Cortex SWD debug interface.

- Support for Apollo MCU family included in Segger J-Link software

- Apollo family EVBs have onboard J-Link interface. Just connect USB.

- All example code provided in Ambiq SDK come with Keil and IAR projects and GCC Makefile

- Keil and IAR downloads with Apollo family support built-in provided by their respective manufacturers

endpoint intelligence

# Appendix

## Apollo3 / Apollo3 Blue Features

| CORE CORE               |                                    |                             |                     | Memory      |             | Blueto     | oth <sup>®</sup> Low Energy          | '            | Sensor Per                                 | ipherals                  |

|-------------------------|------------------------------------|-----------------------------|---------------------|-------------|-------------|------------|--------------------------------------|--------------|--------------------------------------------|---------------------------|

| Arm®                    | Cortex <sup>e</sup> -M4 wit        | h FPU, Up to 96             | MHz                 | 1MB Flash   |             |            | Bluetooth Low<br>Energy 5 Controller |              | 14-bit, 2.67 MS/s<br>15-Channel SAR<br>ADC |                           |

|                         |                                    |                             |                     |             |             |            | Security                             |              | Voltage Cor                                | nparator                  |

| 16KB<br>Flash<br>Memory | Wake-up<br>Interrupt<br>Controller | Power<br>Management<br>Unit | Reset<br>Controller |             | 384KB RAM   |            | luetooth Low<br>nergy Radio          |              | Tempera                                    | ture                      |

|                         |                                    |                             | ·                   |             | DMA         |            |                                      |              | Sens                                       |                           |

| ning                    |                                    |                             | Steppe              | Motor       | Voltage Mor | itoring    | Serial Con                           | nmunica      | tion                                       |                           |

|                         |                                    | Timers                      | Progr               | ammable     | Power-on    | Buck       | 50-<br>Channel                       | UART<br>(x2) | PDM<br>Master                              | I <sup>2</sup> S<br>Slave |

| System<br>Timer/RT      | c                                  | (x8)                        | Contr               | ollers (x8) | Reset       | Converters | GPIO                                 | 1000         | (x1 stereo)                                | (x1)                      |

#### Apollo3 Blue BLE 5 Radio Rx: -93dBm, TX: +4dBm

#### **Ultra-Low Supply Current**

- $6 \,\mu\text{A/MHz}$  executing from flash or RAM at 3.3 V

- 1 μA deep sleep mode (Bluetooth Low Energy Off) with RTC at 3.3 V (Bluetooth Low Energy in SD)

#### High-Performance Arm Cortex-M4 Processor

- Up to 48 MHz nominal clock frequency with 96 MHz performance TurboSPOT Mode

- Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Wake-up interrupt controller with 32 interrupts

#### **Ultra-Low Power Memory**

- Up to 1MB of flash memory for code/data

- Up to 384KB of low power RAM for code/data

- 16KB 2-way Associative/Direct-Mapped Cache

#### **Ultra-Low Power Flexible Serial Peripherals**

- ISO7816 Secure interface

- 1x 2/4/8-bit SPI master interface (MSPI)

- 6x I<sup>2</sup>C/SPI masters for peripheral communication

- 1x I<sup>2</sup>C/SPI slave for host communications

- 2x UART modules with 32-location Tx and Rx FIFOs

- PDM for mono and stereo audio microphones

- 1x 1<sup>2</sup>S slave for PDM audio pass-through

#### **Package Options**

- 5 mm x 5 mm, 81-pin BGA with 50 GPIO

- 3.25 mm x 3.37 mm, 66-pin WLCSP with 37 GPIO

#### 🕲 ambiq

### Apollo3 Blue Plus Features

| CU Core                 |                                    |                             |                     | Memory                   |                   | Bluetoo            | oth <sup>®</sup> Low Energy            | Sensor Per                               | ipherals                          |

|-------------------------|------------------------------------|-----------------------------|---------------------|--------------------------|-------------------|--------------------|----------------------------------------|------------------------------------------|-----------------------------------|

| Arm® C                  | ortex®-M4 with                     | n FPU, Up to 96             | MHz                 |                          | 2MB Flash         | В                  | luetooth Low<br>Energy 5<br>Controller | 14-bit, 1.2<br>15-Char<br>ADC            | nel                               |

|                         |                                    |                             |                     |                          |                   |                    | Security                               | Low Lea<br>Compar                        | - C                               |

| 6KB Flash<br>Cache      | Wake-Up<br>Interrupt<br>Controller | Power<br>Management<br>Unit | Reset<br>Controller |                          | 768KB RAM         |                    | Bluetooth Low<br>Energy Radio          | Tempera                                  |                                   |

| ning                    |                                    |                             | Steppe              | r Motor                  | Voltage           |                    | Serial Commu                           | nication                                 |                                   |

|                         |                                    |                             |                     |                          | voltage           |                    | Senar Commu                            | meation                                  |                                   |

| System<br>Timer/<br>RTC |                                    | Timers/<br>PWM (x8)         |                     | rammable<br>rollers (x8) | Power-on<br>Reset | Buck<br>Converters | 70-Channel U                           | JART<br>(x2) PDM<br>Master<br>(x1stereo) | I <sup>2</sup> S<br>Slave<br>(x1) |

#### **BLE 5 Radio** Rx: -93dBm, TX: +4dBm

#### **Ultra-Low Supply Current**

- $6 \,\mu\text{A}/\text{MHz}$  executing from flash or RAM at 3.3 V

- 1 μA deep sleep mode (Bluetooth Low Energy Off) with RTC at 3.3 V (Bluetooth Low Energy in SD)

#### High-Performance Arm Cortex-M4 Processor

- Up to 48 MHz nominal clock frequency with 96 MHz performance TurboSPOT Mode

- Floating Point Unit (FPU)

- Memory Protection Unit (MPU)

- Wake-up interrupt controller with 32 interrupts

#### **Ultra-Low Power Memory**

- Up to 2MB of flash memory for code/data

- Up to 768KB of low power RAM for code/data

- 16KB 2-way Associative/Direct-Mapped Cache

#### **Ultra-Low Power Flexible Serial Peripherals**

- ISO7816 Secure interface

- 1x 2/4/8-bit SPI master interface (MSPI)

- 6x I<sup>2</sup>C/SPI masters for peripheral communication

- 1x I<sup>2</sup>C/SPI slave for host communications

- 2x UART modules with 32-location Tx and Rx FIFOs

- PDM for mono and stereo audio microphones

- 1x 1<sup>2</sup>S slave for PDM audio pass-through

#### **Package Options**

5.3 mm x 4.3 mm x 0.8 mm, 108-pin BGA with 74 GPIO

ambiq

### Apollo3 Blue Plus Voice-on-SPOT<sup>™</sup> Kit

#### Hardware

#### **Ultra-Low Power**

Apollo3 Blue Plus

#### **High Performance Cortex-M4F Processor**

48 MHz nominal clock frequency with 96 MHz TurboSPOT Mode

#### **Integrated Bluetooth Low Energy**

- RF Sensitivity: -93dBm

- TX Power: +4dBm max

#### **Boards**

- Digital MIC Click Boards Vesper & Memsensing

- Apollo3 mikroBUS Audio Shield

- Apollo3 Blue Plus EVB

### Software

#### Ambiq

- VoS SDK

- AmbiqSuite SDK

#### Communication

- Amazon Mobile Accessory (AMA)

- Google Android TV Voice Service ATVV over BLE

- Audio stream over RTT, AMU2S (SPI to USB)

endpoint intelligence

# **Thank You!**