# **USER'S GUIDE**

# **Apollo4 Family Security**

Ultra-Low Power Apollo SoC Family A-SOCAP4-UGGA05EN v1.3

# **Legal Information and Disclaimers**

AMBIQ MICRO INTENDS FOR THE CONTENT CONTAINED IN THE DOCUMENT TO BE ACCURATE AND RELIABLE. THIS CONTENT MAY, HOWEVER, CONTAIN TECHNICAL INACCURACIES, TYPOGRAPHICAL ERRORS OR OTHER MISTAKES. AMBIQ MICRO MAY MAKE CORRECTIONS OR OTHER CHANGES TO THIS CONTENT AT ANY TIME. AMBIQ MICRO AND ITS SUPPLIERS RESERVE THE RIGHT TO MAKE CORRECTIONS, MODIFICATIONS, ENHANCEMENTS, IMPROVEMENTS AND OTHER CHANGES TO ITS PRODUCTS, PROGRAMS AND SERVICES AT ANY TIME OR TO DISCONTINUE ANY PRODUCTS, PROGRAMS, OR SERVICES WITHOUT NOTICE.

THE CONTENT IN THIS DOCUMENT IS PROVIDED "AS IS". AMBIQ MICRO AND ITS RESPECTIVE SUPPLIERS MAKE NO REPRESENTATIONS ABOUT THE SUITABILITY OF THIS CONTENT FOR ANY PURPOSE AND DISCLAIM ALL WARRANTIES AND CONDITIONS WITH REGARD TO THIS CONTENT, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHT.

AMBIQ MICRO DOES NOT WARRANT OR REPRESENT THAT ANY LICENSE, EITHER EXPRESS OR IMPLIED, IS GRANTED UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT OF AMBIQ MICRO COVERING OR RELATING TO THIS CONTENT OR ANY COMBINATION, MACHINE, OR PROCESS TO WHICH THIS CONTENT RELATE OR WITH WHICH THIS CONTENT MAY BE USED.

USE OF THE INFORMATION IN THIS DOCUMENT MAY REQUIRE A LICENSE FROM A THIRD PARTY UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF THAT THIRD PARTY, OR A LICENSE FROM AMBIQ MICRO UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF AMBIQ MICRO.

INFORMATION IN THIS DOCUMENT IS PROVIDED SOLELY TO ENABLE SYSTEM AND SOFTWARE IMPLEMENTERS TO USE AMBIQ MICRO PRODUCTS. THERE ARE NO EXPRESS OR IMPLIED COPYRIGHT LICENSES GRANTED HEREUNDER TO DESIGN OR FABRICATE ANY INTEGRATED CIRCUITS OR INTEGRATED CIRCUITS BASED ON THE INFORMATION IN THIS DOCUMENT. AMBIQ MICRO RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN. AMBIQ MICRO MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR DOES AMBIO MICRO ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT, AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY, INCLUDING WITHOUT LIMITATION CONSEQUENTIAL OR INCIDENTAL DAMAGES. "TYPICAL" PARAMETERS WHICH MAY BE PROVIDED IN AMBIQ MICRO DATA SHEETS AND/OR SPECIFICATIONS CAN AND DO VARY IN DIFFERENT APPLICATIONS AND ACTUAL PERFORMANCE MAY VARY OVER TIME. ALL OPERATING PARAMETERS, INCLUDING "TYPICALS" MUST BE VALIDATED FOR EACH CUSTOMER APPLICATION BY CUSTOMER'S TECHNICAL EXPERTS. AMBIQ MICRO DOES NOT CONVEY ANY LICENSE UNDER NEITHER ITS PATENT RIGHTS NOR THE RIGHTS OF OTHERS. AMBIQ MICRO PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN SYSTEMS INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR OTHER APPLICATIONS INTENDED TO SUPPORT OR SUSTAIN LIFE, OR FOR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE AMBIQ MICRO PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR. SHOULD BUYER PURCHASE OR USE AMBIO MICRO PRODUCTS FOR ANY SUCH UNINTENDED OR UNAUTHORIZED. APPLICATION, BUYER SHALL INDEMNIFY AND HOLD AMBIQ MICRO AND ITS OFFICERS, EMPLOYEES, SUBSIDIARIES, AFFILIATES, AND DISTRIBUTORS HARMLESS AGAINST ALL CLAIMS, COSTS, DAMAGES, AND EXPENSES, AND REASONABLE ATTORNEY FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PERSONAL INJURY OR DEATH ASSOCIATED WITH SUCH UNINTENDED OR UNAUTHORIZED USE, EVEN IF SUCH CLAIM ALLEGES THAT AMBIO MICRO WAS NEGLIGENT REGARDING THE DESIGN OR MANUFACTURE OF THE PART.

# **Revision History**

| Revision | Date              | Description                                                                                                                                                                                                                     |  |

|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | November 19, 2021 | Initial release                                                                                                                                                                                                                 |  |

| 1.1      | August 1, 2022    | <ul> <li>Updated content in section 7 Run-Time Security Services</li> <li>Updated Table 9-9 NVM Access Protection Field Description</li> </ul>                                                                                  |  |

| 1.2      | October 19, 2022  | <ul> <li>Updated document template</li> <li>Updated Figure 6-1 Table for LCS Defaults</li> <li>Added note on section 8 Factory Default SoC Configuration</li> </ul>                                                             |  |

| 1.3      | July 5, 2023      | <ul> <li>Updated and added notes in section 2 Introduction</li> <li>Added new content in section 8 Factory Default SoC Configuration</li> <li>Updated references to "Apollo4 and Apollo4 Blue" with "Apollo4 Family"</li> </ul> |  |

# **Reference Documents**

| Document ID       | Description                                                 |

|-------------------|-------------------------------------------------------------|

| A-SOCAP4-UGGA01EN | Apollo4 Family Provisioning, Update, and Tools User's Guide |

| A-SOCAP4-UGGA02EN | Apollo4 Family Secure Update User's Guide                   |

|                   |                                                             |

# **Table of Contents**

| 1. | . Terminology                                  | 8    |

|----|------------------------------------------------|------|

| 2. | . Introduction                                 | 11   |

| 3. | . Apollo4 Secure Boot Overview                 | 13   |

|    | 3.1 Secure Boot Functional Components          |      |

|    | 3.1.2 Secure Boot Loader (SBL) (Upgradeable)   | . 14 |

|    | 3.1.3 Customer Secure Bootloader               | . 15 |

| 4. | . Security Life Cycle States                   | 16   |

|    | 4.1 Chip Manufacturer (CM) LCS                 | . 16 |

|    | 4.2 Device Manufacturer (DM) LCS               | . 16 |

|    | 4.3 Secure Enabled (SE) LCS                    |      |

|    | 4.4 Return Merchandise Authorization (RMA) LCS | . 16 |

| 5. | . Secure Boot Mode                             | 17   |

|    | 5.1 OEM Certificates and Certificate Chains    |      |

|    | 5.2 Certificate Formats                        |      |

|    | 5.2.1 Key Certificates                         |      |

| 6. | . Debug Support                                | 21   |

|    | 6.1 Secure Debug Certificates                  | . 22 |

|    | 6.2 Secure Debug Certificate Handling          |      |

| 7. | . Run-Time Security Services                   | 24   |

| 8. | . Factory Default SoC Configuration            | 25   |

| 9. | SecureSPOT Configuration                       | 27   |

|    | 9.1 One Time Programmable (OTP) Memory         | . 27 |

| 9.2 OEM Keys/Secure Assets                        | 28 |

|---------------------------------------------------|----|

| 9.2.1 Asymmetric Root of Trust                    | 28 |

| 9.2.2 Symmetric Keys                              |    |

| 9.2.3 Custom Key Storage                          | 29 |

| 9.3 OEM Security Policy                           |    |

| 9.3.1 Configuration of Secure Boot                | 30 |

| 9.3.2 Secondary Bootloader Configuration          |    |

| 9.3.3 INFO Space Protections                      |    |

| 9.3.4 Update Configuration                        |    |

| 9.3.5 Wired Interface Configuration               |    |

| 9.3.6 NVM Access Protection                       |    |

| 9.3.7 Symmetric Keybank Protections               |    |

| 9.3.8 Debug Control                               |    |

| 9.4 OEM Infospace (INFO0) Configuration           |    |

| 9.4.1 Signature                                   |    |

| 9.4.2 Customer Trims                              |    |

| 9.4.3 Wired UART Config                           |    |

| 9.5 Security Version                              |    |

| 9.5.1 Memory Reservation                          |    |

| 9.5.2 Enable RMA Override                         |    |

| 9.5.3 Secure Debug Certificate Locations          |    |

| 9.5.4 Main Application Location (Non-Secure Boot) |    |

| 9.5.5 Certificate Criditi Location (Secure Boot)  | 30 |

| 10. Configuring Secure Boot Mode                  | 37 |

| 11. Transition to Secure LCS                      | 38 |

| 11.1 Generating the Provisioning Blob             | 30 |

|                                                   |    |

| 11.2 Provisioning the Device                      | 40 |

| 12. Transition to RMA LCS                         | 42 |

| 13. Image Updates                                 | 44 |

| 13.1 General Update (OTA) Process                 | 45 |

| 13.2 Secure Bootloader Image Updates              |    |

| 13.2 Secure bootiouder image opuates              | 45 |

| 14. Appendix                                      | 46 |

| 14 1 OTP Configuration                            | 46 |

# **List of Tables**

| Table 1-1 Terminology                                                    | 8  |

|--------------------------------------------------------------------------|----|

| Table 5-1 OEM Root and Key Certificate Structure                         | 19 |

| Table 5-2 Content Certificate Structure                                  | 19 |

| Table 9-1 Asymmetric Root of Trust Field Descriptions                    | 28 |

| Table 9-2 Symmetric Keys Field Descriptions                              | 28 |

| Table 9-3 Custom Key Storage Field Descriptions                          | 29 |

| Table 9-4 Secure Boot Field Descriptions                                 | 30 |

| Table 9-5 Secondary Bootloader Field Description                         | 30 |

| Table 9-6 INFO Space Protections Field Description                       | 30 |

| Table 9-7 Update Configuration Field Description                         | 31 |

| Table 9-8 Wired Interface Configuration Field Description                | 31 |

| Table 9-9 NVM Access Protection Field Description                        | 32 |

| Table 9-10 Symmetric Keybank Protection Field Description                | 32 |

| Table 9-11 LCS Conditions and Results                                    | 32 |

| Table 9-12 Debug Control Field Description                               | 34 |

| Table 9-13 Signature Field Description                                   | 34 |

| Table 9-14 Customer Trims Field Description                              | 34 |

| Table 9-15 Wired UART Config Field Description                           | 35 |

| Table 9-16 Security Version Field Description                            | 35 |

| Table 9-17 Memory Reservation Field Description                          | 35 |

| Table 9-18 Secure Debug Certificate Locations Field Description          | 36 |

| Table 9-19 Main Application Location (Non-Secure Boot) Field Description | 36 |

| Table 9-20 Certificate Chain Location (Secure Boot) Field Description    | 36 |

| Table 14-1 OTP Region Start Address: 0x400C2000                          | 46 |

# **List of Figures**

| Figure 3-1 Apollo4 Secure Boot Architecture                        | 13 |

|--------------------------------------------------------------------|----|

| Figure 3-2 Secure Boot Loader (SBL) Flow                           | 15 |

| Figure 5-1 Supported Certificate Chains for OEM Content Management | 18 |

| Figure 6-1 Table for LCS Defaults                                  | 21 |

| Figure 6-2 Relationship Between Secure Debug Certificates          | 22 |

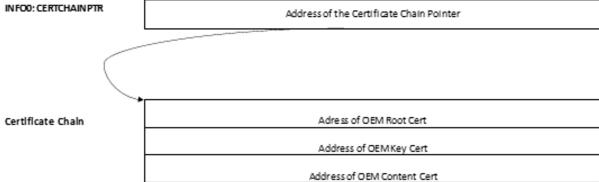

| Figure 9-1 OEM Certificate Chain Pointers                          | 36 |

| Figure 11-1 OEM Provisioning Blob Generation                       | 39 |

| Figure 11-2 OEM Provisioning Blob Generation                       |    |

# **Terminology**

This section defines the abbreviation and terminology used in this document.

Table 1-1: Terminology

| Abbreviation | Definition                         | Meaning                                                                                                                                                                                                                                                                                      |

|--------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AES          | Advanced Encryption Standard       |                                                                                                                                                                                                                                                                                              |

|              | BootROM                            | This is a ROM program that originally boots on reset and provides the initial immutable RoT.                                                                                                                                                                                                 |

|              | Certificate Chain                  | A dependent sequence of certificates that together can be used validate content in the SoC memory. The certificate chain is composed of key certificates and a content certificate. The advantage of a chain is that some of the links can change without installing a completely new chain. |

| CM LCS       | Chip Manufacturing LCS             | Ambiq acting with the fabrication, packaging, and test house partners (e.g., ICV) is considered the Chip Manufacturer. In this LCS, the SoC is mostly open and ready for initial provisioning with Ambiq security assets.                                                                    |

|              | Content Certificate                | A certificate used to load and validate software components.                                                                                                                                                                                                                                 |

| DCU          | Debug Control Unit                 | CryptoCell-312 mechanism to control the debug mechanism and feature enablement.                                                                                                                                                                                                              |

| DM LCS       | Device Manufacturing LCS           | These are typically Ambiq's direct customers and consumers of the Apollo4 SoCs (e.g., OEM). In this LCS, the customer provisions their security policy and assets.                                                                                                                           |

| НВК          | Hash of the Public Key             | Ambiq uses the Dual scheme:  Hbk0: A 128-bit truncated SHA-256 digest of the ICV PubKB0. Hbk1: A 128-bit truncated SHA-256 digest of the OEM PubKB1.                                                                                                                                         |

| НМАС         | Hashed Message Authentication Code |                                                                                                                                                                                                                                                                                              |

| HUK          | Hardware Unique Key                | This is a 256-bit SoC-unique AES key that is used as the root for deriving all SoC-specific keys.                                                                                                                                                                                            |

| ICV          | Integrated Chip Vendor             | ICV (e.g., CM) is Ambiq acting with the fabrication, packaging, and test house partners.                                                                                                                                                                                                     |

Table 1-1: Terminology (Continued)

| Abbreviation | Definition                       | Meaning                                                                                                                                                                                                                                                              |

|--------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INFO0        | InfoSpace Region #0              | This is an area of memory inside the SoC that is designed to be programmed by the OEM and hold customer visible attributes include security assets.                                                                                                                  |

| INFO1        | InfoSpace Region #1              | This is an area of memory inside the SoC that is design to be programmed by the ICV to hold SoC trims and security assets.                                                                                                                                           |

| IPT          | ICV Provisioning Tool            | A tool used by Ambiq's internal teams (software, validation, production test) to provision the secure assets of the SoC.                                                                                                                                             |

| Kce          | OEM Code Encryption Key          | 128-bit AES key that is used to decrypt software images as part of the Secure Boot process.                                                                                                                                                                          |

| Kceicv       | ICV Code Encryption Key          | 128-bit AES key that is used to decrypt software images as part of the Secure Boot process.                                                                                                                                                                          |

| Кср          | OEM Provisioning Master Key      | 128-bit AES key that is used for the OEM asset provisioning flow.                                                                                                                                                                                                    |

|              | Key Certificate                  | A certificate used to validate the next certificate in a chain.                                                                                                                                                                                                      |

| Kpicv        | ICV Provisioning Master Key      | 128-bit AES key that is used for the ICV asset provisioning flow.                                                                                                                                                                                                    |

| Krtl         | Platform key                     | An ICV key placed in the RTL. It is used for provisioning during production life-cycle states.                                                                                                                                                                       |

| LCS          | Life Cycle State                 | The state of the SoC that determines the level of security and access to features.                                                                                                                                                                                   |

| OEM          | Original Equipment Manufacturer  | These are typically Ambiq's direct customers and consumers of the Apollo4 SoCs (e.g., DM).                                                                                                                                                                           |

| ОРТ          | OEM Provisioning Tool            | A set of example scripts designed to run on a Linux OS computer for the purpose of providing an example of the OEM provisioning flow. It is envisioned that these scripts will be adopted by the OEM into their production flow.                                     |

| ОТР          | One Time Programmable memory     | This is an area of memory in the Apollo4 that can be programmed only once during provisioning. The OPT burns OEM keys and assets to the SoC OTP in DM LCS.                                                                                                           |

| PKI          | Public Key Infrastructure        | A set of roles, policies, hardware, software and procedures needed to create, manage, distribute, use, store and revoke digital certificates and manage public-key encryption.                                                                                       |

| RMA LCS      | Return Merchandise Authorization | This is the process of returning a faulty SoC. The RMA LCS is a special state that does not allow recovery of the SoC. As the RMA LCS is entered, the security assets for the ICV and OEM are erased.                                                                |

| RoT          | Root of Trust                    | This is the original source that can always be trusted within a cryptographic system.                                                                                                                                                                                |

| RSA          | Rivest – Shamir – Adleman        | An algorithm used by modern computers to encrypt and decrypt messages. It is an asymmetric cryptographic algorithm. Asymmetric means that there are two different keys. This is also called public key cryptography, because one of the keys can be given to anyone. |

| SBR          | Secure BootROM                   | This is actually a misnomer. The SBR is code found in a locked down region of MRAM. It is the first stage of processing after the actual BootROM in the Apollo4. This architecture was done to reduce the risk on the Rev B silicon.                                 |

Table 1-1: Terminology (Continued)

| Abbreviation | Definition                      | Meaning                                                                                                                                                                                                                    |

|--------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SE LCS       | Secure Enable LCS               | This is the state when the SoC is fully secured and content is authenticated and updated according to the established OEM security policy. Debugging is disabled. This is the proper state when the SoC is "in the field". |

| Secure OTA   | Secure Over the Air programming | This is the process of authenticating and installing a "blob" of data that has been delivered to the SBL. This blob could be received over any radio (air) or wired interface (I <sup>2</sup> C, SPI, SWO, UART).          |

| TEE          | Trusted Execution Environment   |                                                                                                                                                                                                                            |

| Wire Update  |                                 | This is the process and protocol of receiving a sequence of packets over a wired interface (I <sup>2</sup> C, SPI, or UART).                                                                                               |

2

# Introduction

#### **NOTES:**

- This document assumes "public side crypto enabled devices".

- This document applies to the Apollo4 family of SoCs. Any reference to Apollo4 assumes any device unless explicitly stated otherwise.

- References to /tools/apollo4b\_scripts/ directory applies to /tools/apollo4l\_scripts/ directory unless explicitly stated otherwise.

- Apollo4 and Apollo4 Plus devices utilize the same /tools/apollo4b\_scripts/ directory. Apollo4

Lite and Blue Lite devices use the /tools/apollo4l\_scripts/ directory.

- References to register documentation within AmbiqSuite, such as /mcu/apollo4b/regs/, apply for Apollo4 Plus and Apollo4 Lite, and are found within their respective directories in AmbiqSuite/mcu/.

The security features of the Apollo4 system on chip (SoC) enable a trusted execution environment for resource constrained wearable and IoT devices. The Apollo4 supports the Arm Platform Security Architecture (PSA) and provides a robust system level security leveraging Ambiq's SecureSPOT™ technology. The Apollo4 security includes Arm Cryptocell hardware cryptographic acceleration, One-Time Programmable (OTP) memory, a hardened BootROM, and a secure boot firmware in MRAM to ensure a complete end-to-end secure environment for customer applications. The Apollo4 establishes and maintains a Root-of-Trust (RoT) throughout SoC boot, reset, and firmware upgrade flows.

The specific security features supported by the Apollo4 SoC include:

- Secure Boot using Root-of-Trust in OTP

- Secure Over-the-Air (OTA) Updates

- Secure Wired Updates over I<sup>2</sup>C, SPI, or UART

- Secure Key Storage in OTP

- Support for Secure and Non-secure modes of operation

- Lifecycle States (LCS) management

- Secure Debug using Secure Debug Certificates which provide selective debug controls and/ or transition to RMA LCS.

- Support for Certificate Chain based authentication for customer image(s) to run, which are verified using PKI rooted in on chip RoT.

- Hardware Crypto Acceleration and True Random Number Generator (TRNG)

- CRC32

- Tools for asset provisioning during manufacturing

- Support for customer specific secondary boot loader (to be executed after Ambiq Secure Bootloader)

This document provides an overview to new customers on how to work with the SecureSPOT features of the Apollo4 SoCs. This document assumes the customer will supplement the information provided here with the Reference Documents noted earlier. Information presented in those documents is key to understanding this document in depth.

The Apollo4 SecureSPOT includes cryptographic hardware acceleration, one-time programmable memory, customer trimming, Secure BootROM, Secure Bootloader, runtime security API, and provisioning tools designed to operate as a complete package to ensure protection of the reader's assets.

The first part of this document focuses on the Apollo4 Security infrastructure overview, and second part on configuring, provisioning and usage.

The document will cover the following important topics:

- Apollo4 Security infrastructure

- Apollo4 Secure Boot overview

- Security Life Cycle States (LCS)

- Secure Boot Mode

- Debug Support

- Run Time Security Services

- Configuration, Provisioning & Usage

- Default SoC Configuration

- OTP Configuration

- OEM InfoSpace (INFO0) Configuration

- Configuring Secure Boot Mode

- Transition to Secure LCS

- Transition to RMA LCS

- Image Updates

# **Apollo4 Secure Boot Overview**

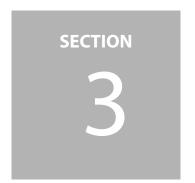

At a high level, the Apollo4 Secure Boot architecture and features are modeled in Figure 3-1.

Figure 3-1: Apollo4 Secure Boot Architecture

#### Immutable Root of Trust

- Secure Boot ROM

- · Hardware enforced

- Initiates chain of trust firmware validation using secure boot certificates

- Hardware crypto backed

- Lifecycle State management

- Establishes debug lockouts to prevent debug/tracing/interrupts during secure boot critical section execution based on secure debug certificates

- Hardware OTP key storage and security policy configuration

The base of the security model is the Root-of-Trust in OTP memory which is provisioned during chip and device manufacturing. Upon a power-cycle, the BootROM validates SoC trims and security settings, and then authenticates the Secure BootROM (SBR) in MRAM. Control is then passed to the Secure BootROM. The Secure BootROM provides for CM and DM state provisioning of the security assets and policies in the OTP memory. The SBR also performs Certificate Chain based verification of the Secure Bootloader (SBL) and processing of Secure Debug certificates. The Secure Bootloader includes support for OTA firmware updates, self-upgrade, wired updates, certificate chain updates, key revocation, trim patch updates, and certificate chain-based authentication of optional customer secondary bootloaders or customer main images.

# 3.1 Secure Boot Functional Components

## 3.1.1 Secure BootROM (Immutable)

- Authentication of SBL using Secure Boot certificate to continue to boot flow

- ICV/OEM Provisioning support

- Life Cycle Management

- Secure Debug Certificate Processing

# **3.1.2** Secure Boot Loader (SBL) (Upgradeable)

- Authentication of Ambig and Customer images

- Secure OTA

- Value Added Services

- Support for Non-secure and Secure mode of operation

- Enforcement of OTP security policies

- Wired Updates

- Trim Updates

- SBL Updates

- SBL can be in-field updated using secure OTA

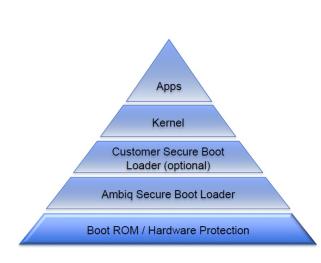

The overall flow is shown in Figure 3-2 on page 15.

Figure 3-2: Secure Boot Loader (SBL) Flow

### 3.1.3 Customer Secure Bootloader

- Enhanced/Custom Services

- Proprietary Cryptographic Algorithms

- External Memory Device Drivers

- Custom Interface Drivers or Protocols

4

# **Security Life Cycle States**

# 4.1 Chip Manufacturer (CM) LCS

Ambiq acting with our fabrication, packaging and test house partners is considered the Chip Manufacturer. In CM LCS, the SoC is mostly open and ready for initial provisioning. In CM LCS, Ambiq provisions our secret assets (root keys), our Root of Trust and our security policy.

# 4.2 Device Manufacturer (DM) LCS

Ambiq's customers are considered Device Manufacturers. DM LCS is the initial state of the Apollo4 devices when received by customers. Ambiq provides tools that allow customers to provision their own secret assets, Root of Trust, and security policy. The customer can elect to operate the Apollo4 in non-secure mode and stay in DM LCS perpetually or they can operate in secure mode in Secure Enabled LCS.

# 4.3 Secure Enabled (SE) LCS

SE LCS is the state when the SoC is fully secured and content is authenticated and updated according to the established customer security policy. Debugging is disabled. This is the proper state of a fully secure device "in the field."

# 4.4 Return Merchandise Authorization (RMA) LCS

RMA LCS is activated when a faulty SoC needs to be returned to Ambiq for analysis and debug. RMA LCS is a special state and does not allow the recovery of the SoC. As RMA LCS is entered both Ambiq and customer security assets are erased.

5

# **Secure Boot Mode**

The Apollo4 SoC defaults as a "Secure" SKU, although it may be released as a "Non-Secure" SKU in the future. For the Secure SKU, there are two security "modes" which can be provisioned by the customer using OTP, as part of provisioning:

- Non-Secure Mode

- Secure boot and some other secure services are not supported.

- Secure Mode

- Secure boot and other secure services are supported.

An unprogrammed chip defaults to Non-secure mode.

The Apollo4 can be configured for Secure mode in both DM LCS, and Secure LCS. When configured for secure boot, SBL validates the boot images using pre-installed certificate chain, and any tampering or corruption of image would result in a boot failure.

**NOTE:** When it comes to Ambiq installed assets (e.g., SBL), it is always verified using the same certificate chain approach, irrespective of whether Secure Mode is enabled or not.

# **5.1 OEM Certificates and Certificate Chains**

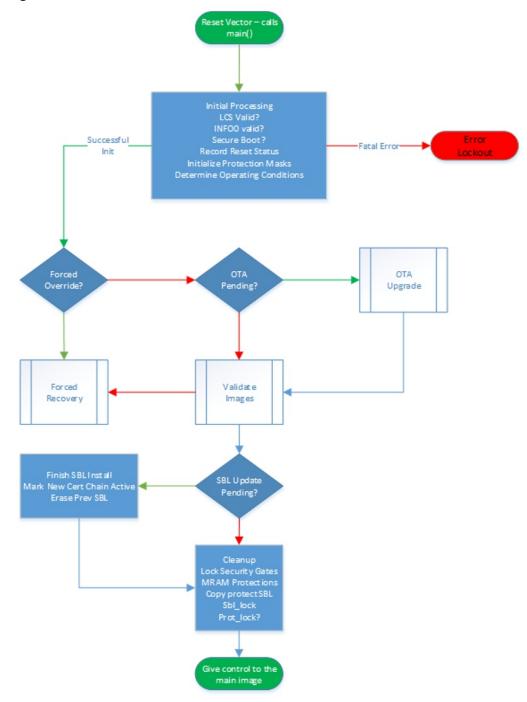

The Apollo4 security features support certificate chains for OEM content management as shown in Figure 5-1 on page 18. The Root-of-Trust for these chains is the same truncated public key hash in OTP mentioned above.

There are three certificates in the chain:

- OEM Root Certificate

- OEM Key Certificate

- OEM Content Certificate

Figure 5-1: Supported Certificate Chains for OEM Content Management

## 5.1.1 Verifying the Certificate Chain

Use the following procedure to verify the certificate chain:

- 1. Retrieve the public key from the certificate and calculate its hash.

- For the OEM Root Certificate compare the hash to the HBK1.

- For all other certificates compare the hash value to value stored from the previous certificate.

- 2. Verify the RSA signature:

- a. Calculate the hash of the certificate excluding the signature.

- b. Use the public key in the certificate to decrypt the signature, recreating the hash value.

- c. Compare the two hash values.

- 3. Check the software version information.

#### **NOTE:**

- The software version for the chain must be equal or larger than the software version stored in OTP.

- When in DM LCS, the verification step binding the Root Certificate to the RoT in OTP is skipped, as RoT is not programmed yet.

## 5.2 Certificate Formats

## **5.2.1** Key Certificates

The following structure is used for OEM Root and Key certificates.

Table 5-1: OEM Root and Key Certificate Structure

| Structure              | Field          | Description                                                                                    |

|------------------------|----------------|------------------------------------------------------------------------------------------------|

| Certificate Header     | magicNumber    | Magic number to validate the certificate.                                                      |

|                        | certVersion    | Certificate version to validate the certificate.                                               |

|                        | certSize       | Offset in words to the Certificate signature. And number of software components, if any exist. |

|                        | certFlags      | Bit field interpreted according to the certificate type.                                       |

| Certificate Public Key | N              | 3072-bit public key in big endian format                                                       |

|                        | Np             | 160-bit Barrett n' value                                                                       |

| Certificate Body       | swVer          | Software version associated with certificate                                                   |

|                        | nextPubKeyHash | SHA256 hash result                                                                             |

| Certificate Signature  | sig            | 3072-bit RSA PSS signature                                                                     |

## **5.2.2** Content Certificate

The Content Certificate contains information about one or more images that need to be verified. The certificate contains an entry for each image, which has the address of the image in NVM, the size of the image, and the Hash corresponding to the image (for authentication). By convention, the content certificate Image[0] always corresponds to the main application image. Thus, upon successful verification, control is passed to this image.

Content Certificate can also contain optional protection configuration, instructing the SBL to apply either copy or write protection attributes to the images before handing off control to the main image.

Table 5-2: Content Certificate Structure

| Structure              | Field       | Description                                                                                   |

|------------------------|-------------|-----------------------------------------------------------------------------------------------|

| Certificate Header     | magicNumber | Magic number to validate the certificate.                                                     |

|                        | certVersion | Certificate version to validate the certificate.                                              |

|                        | certSize    | Offset in words to the Certificate signature. And number of software components, if any exist |

|                        | certFlags   | Bit field interpreted according to the certificate type.                                      |

| Certificate Public Key | N           | 3072-bit public key in big endian format                                                      |

|                        | Np          | 160-bit Barrett n' value                                                                      |

Table 5-2: Content Certificate Structure (Continued)

| Structure             | Field            | Description                                  |

|-----------------------|------------------|----------------------------------------------|

| Content               | swVer            | Software version associated with certificate |

|                       | nonce            | pseudo-random arbitrary number               |

|                       | imageRec[]       | array of image records                       |

|                       | imageHash        | SHA256 hash result                           |

|                       | IoadAddr         | MRAM address to load image                   |

|                       | imageMaxSize     | Max Image size in bytes                      |

|                       | isAesCodeEncUsed | Image is encrypted (Not Supported)           |

|                       | CopyProtect      | Protect the MRAM sectors from Read           |

|                       | WriteProtect     | Protect the MRAM sectors from Write          |

| Certificate Signature | sig              | 3072-bit RSA PSS signature                   |

# **Debug Support**

The Apollo4 has hardware support for selective enabling of pre-identified debug features using Arm Cryptocell Debug Control Unit (DCU).

DCU controls are defined as 'qualified' bitmasks – with predefined significance for bits (see Global DCU Enabled in Figure 6-1). At the hardware level, each qualified bit is triple encoded for added security (raw DCU mask).

Hardware raw DCU bits Raw DCU bits (CRYPTO->HOSTDCU\*2-3) are triple encoded: b'101 enables a feature, while b'010 disables it.

The following controls available for the raw DCU masks:

- Enable Bitmask (control individual debug feature accessibility)

- Fixed Default Values based on LCS

- Lock Bitmask (once locked, the corresponding DCU bit cannot be modified till POI)

- OTP configuration to lock the state of DCU (OTP LOCKMASK\*)

Figure 6-1: Table for LCS Defaults

|         |                          | Enabled                                 | 020000000000000000000000000000000000000 | Unlocke                                                         | d (Free to change)               | 1/2                          |

|---------|--------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------------------|----------------------------------|------------------------------|

|         | H                        | Disabled                                |                                         | Can be locked for further changes based on OEM controlled OTP s |                                  |                              |

|         |                          |                                         |                                         |                                                                 |                                  |                              |

|         | 49                       |                                         | Default                                 |                                                                 |                                  |                              |

|         | Debug Control            | DM                                      | Secure                                  | RMA                                                             | Global DCU enable<br>(Qualified) | Actual DCU bit with encoding |

|         | CPU Debug - Invasive     |                                         |                                         |                                                                 | 1                                | [66:64]                      |

|         | CPU Debug - Non-invasive |                                         |                                         |                                                                 | 2                                | [69:67]                      |

|         | CPU Tracing              |                                         |                                         |                                                                 |                                  |                              |

|         | ETM                      |                                         |                                         |                                                                 | 3                                | [72:70]                      |

|         | ITM                      |                                         |                                         |                                                                 | 2                                | [69:67]                      |

| Пе      | TPIU/SWO                 |                                         |                                         |                                                                 | 4                                | [75:73]                      |

| Runtime | DWT                      |                                         |                                         |                                                                 | 4                                | [75:73]                      |

| Bu      | Perf Cnt / Energy Mon    |                                         |                                         |                                                                 | 5                                | [78:76]                      |

|         | Cache Debug              |                                         |                                         |                                                                 | 6                                | [81:79]                      |

|         | System Debug             | 000000000000000000000000000000000000000 | 77.77.77.77                             |                                                                 |                                  |                              |

|         | SWD                      |                                         |                                         |                                                                 | 11                               | [96:94]                      |

|         | ETB                      |                                         |                                         |                                                                 | 13                               | [102:100]                    |

|         | TPIU/Trace Port Output   |                                         |                                         |                                                                 | 14                               | [105:103]                    |

### **Enabling Debugging of the Apollo4 SoCs While in Secure LCS**

In order to override default DCU values (based on LCS) and locking (based on OTP configuration), the customer must load a Secure Debug Certificate into NVM.

# **6.1** Secure Debug Certificates

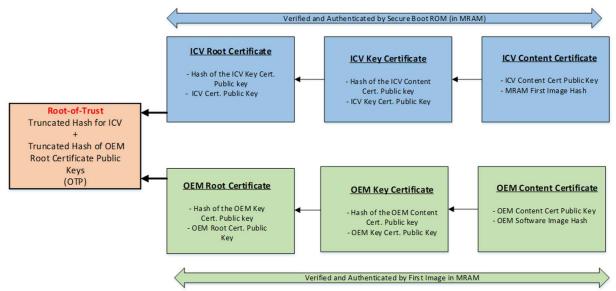

Secure Debug Certificates are a set of two or three level certificates which contain public keys and authentication values. Figure 6-2 shows the relationship between the certificates.

Figure 6-2: Relationship Between Secure Debug Certificates

**OEM Developer Debug Certificate** - OEM Debug Developer Certificate Public Key (Verified using hash in Enabler Cert) - OEM DCU Mask - SOC-ID - Certificate Signature (Signed using **OEM** Debug Developer Certificate Private Key) **OEM Debug Enabler Certificate** - Hash of the Debug Developer Certificate Public Key bler Cert. Public Key (Verified using - OEM DCU Mask and Lock Bits / RMA Configuration - Certificate Signature (Signed using OEM Debug Root-of-Trust Truncated Hash for ICV **OEM Debug-Key Certificate** Truncated Hash of OEM - Hash of the Debug Enabler Certificate Public Key Root Certificate Public - OEM Root Public Key (Verified using RoT Hash) Keys Certificate Signature (Signed using OEM Root (OTP) Private Key)

OEM Debug / RMA Certificate

For the two-level SD certificate scheme, the chain order is:

enabler debug certificate (signed using OEM Root Key) → developer debug certificate.

For the three-level SD certificate chain order is

key certificate (signed using OEM Root Key) → enabler debug certificate → developer debug certificate.

The Key certificate is protected by the software certificate version (and hence can be revoked).

Ambig recommends use of three level certificate chain as depicted here.

The function of each certificate in a three level Certificate is as follows:

- OEM Debug Key Certificate

- Signed by OEM's Root Key (Hash Provisioned in OTP)

- Contains the Hash of Public Key used to verify the Enabler Debug Cert

- OEM Debug Enabler Certificate

- Signed by Enabled Debug Cert Key (Hash in Key Cert)

- Contains the Hash of Public Key used to verify the Developer Debug Cert

- Defines the subset of DCU bits open for editing by Developer

- Overrides the DCU lock mask (supersedes the OTP configuration)

- Applicable only to the LCS for which it is created

- Also used for transition to RMA LCS (see next section)

- OEM Developer Debug Certificate

- Signed by Developer Debug Cert Key

- Defines the actual DCU overrides

- Specific to a chip (SOCID) when in Secure LCS

Refer to the *Apollo4 Family Provisioning, Update, and Tools User's Guide A-SOCAP4-UGGA01EN* for details on how to generate Secure Debug or RMA Certificates.

# **6.2** Secure Debug Certificate Handling

As mentioned before, the customer must provide a mechanism to download the Secure Debug Certificate (SD Cert) on the device in production application. If enabled, Ambiq Secure Bootloader provides a means to download an SD Cert using wired interface, but OEM Security Policies are enforced for the download.

The location for the SD Certs are specified using INFO0 configuration. A subsequent Reset after installing the SD Cert will make the Debug overrides effective. Once installed, the SD Certs remain effective, until they are removed. The Debug overrides are in place till POI (even if the SD Certs is removed before next reset).

SD Certs are chip specific, when in Secure LCS and the 256b SOC-ID must be accessible to read through HAL API.

# **Run-Time Security Services**

AmbiqSuite relies on Arm CryptoCell engine to provide hardware acceleration for various security services to the main application.

Access to these services is provided through Run-time Software Library – maintained as part of open source effort at TrustZone CryptoCell-312 runtime library from Arm, which should be ported to respective OEM infrastructure. It supports Arm MBed™ TLS APIs to access the underlying hardware acceleration.

- Supported Algorithms: This is a non-exhaustive list of algorithms supported. (Refer to Arm® TrustZone® CryptoCell-312 documentation for reference)

- Symmetric Key

- AES 128/192/25

- DES/TDES 64/128/192

- AES MAC 128/192/256

- AES-CCM 128/192/256

- Asymmetric Key

- RSA PKCS#1 2048/3072

- ECC

- DH

- Hash / HMAC

- SHA1, SHA2 (SHA224, SHA256, SHA384, SHA512)

- MD5

- TRNG

**NOTE:** Weak cryptographic algorithms including DES, TDES, SHA1, and MD5 are supported for legacy purposes only. Ambig recommends against their use.

8

# Factory Default SoC Configuration

Ambig ships the SoC in a factory default configuration as follows:

- Device Manufacturing (DM) LCS

- The customer's OTP space is not provisioned and set to 0's

- Device boots in non-secure mode

- Main image assumed at default (0x18000) address

- Debugger is open after Ambig bootloader exits

- Debugger not allowed during Ambig bootloader

- Default wired connections for Apollo4, Apollo4 Plus devices both Blue and non-Blue:

- GPIO60 for TX

- GPIO47 for RX

- For Apollo4 and Apollo4 Plus (Blue and non-Blue), by default Wired Host connection is enabled with UARTO, GPIO47 as Rx, and GPIO60 as Tx, no CTS/RTS, and a Baudrate of 115200. In addition, Secure Bootloader (SBL) will timeout after 500 msec

- Default wired connections for Apollo4 Blue Lite:

- GPIO13 for TX

- GPIO11 for RX

- UART Module is Module 2

- For Apollo4 Blue Lite, by default, the Wired Host connection is enabled with UART2, GPIO11 as RX, and GPIO13 as TX, no CTS/RTS, and a Baudrate of 115200. In addition, Secure Bootloader (SBL) will timeout after 500 msec.

- Default wired connections for Apollo4 Lite:

- GPIO54 for TX

- GPIO11 for RX

- UART Module is Module 2

- For Apollo4 Lite, by default, the Wired Host connection is enabled with UART2,

GPIO11 as RX, and GPIO54 as TX, no CTS/RTS, and a Baudrate of 115200. In addition,

Secure Bootloader (SBL) will timeout after 500 msec.

- INFO0 can be programmed with tools provided in the AmbiqSuite SDK to generate (create\_info0.py) and program INFO0 (jlink-prog-info0.txt)

Default Factory parts boot in non-secure mode without any further configuration. The main image (or secondary bootloader) can be programmed and run from default (0x18000) address in non-volatile memory. Device can be used for development and non-secure testing without any further provisioning, thus INFO0 can be programmed – but is not necessary to get started.

The INFO0 and OTP programming overrides many of the default settings to allow the customization of security policy and assets.

**NOTE:** GPIO60 is unavailable on the Apollo4 Blue Plus KXR package, part number AMA4B2KP-KXR. INFO0 and OTP must be programmed via the SWD debugger interface before using UART wired updates. Reference *Section 4 of A-SOCAP4-UGGA01EN, Apollo4 Family OEM Provisioning, Update, and Tools User's Guide,* for more details.

# **SecureSPOT Configuration**

There are two memory areas that are open to the customer for configuration of the Secure-SPOT features: One Time Programmable (OTP) and INFO0.

# 9.1 One Time Programmable (OTP) Memory

OTP is just like it sounds. OTP memory bit cells can be programmed from 0 to 1 while in DM LCS, but 1 to 0 is not possible. It can only be configured once and then permanently retains the configuration for the life of the part (or until RMA LCS when some of it is erased). This is done as a security measure to protect against tampering and other types of intrusions.

OTP is typically configured in a batch as part of provisioning at OEM device manufacturing.

As an alternative, it is also possible to manually and partially program the OTP, while still in DM LCS. All OTP area fields that get programmed as part of provisioning, are writable in DM LCS and thus can be provisioned programmatically (through OTP HAL API) if desired <sup>1</sup>. Transitioning OTP area bits from 0 to 1 is a one way operation.

Note that in all cases provisioning of RoT also results in DM to SE LCS transition and most of the fields are no longer writable in SE LCS.

The most up to date documentation of the OTP fields is provided along with the AmbiqSuite SDK here: /mcu/apollo4b/regs/pages/am\_mcu\_apollo4b\_otp.html

In general, OTP contains the following:

Root of Trust (RoT)

<sup>&</sup>lt;sup>1</sup>As long as the partial provisioning configuration is subset of full provisioning data, even a partially provisioned part can accept DM Provisioning step for Secure LCS transition.

- Hardware Keys

- OEM Symmetric Key used to authenticate the provisioning tools (KCP)

- OEM Symmetric Key used for encryption/description (KCE)

- OEM Security Policy Selections (OTP\_SECURITY and OTP\_SEC\_POL)

- Debug Control Unit (DCU) Overrides (OTP\_DCU\_DISABLEOVERRIDE)

- Wired Update Configuration (OTP\_BOOT\_OVERRIDE and OTP\_WIRED\_CONFIG)

- OEM Key Assets

Further documentation of the meaning of these fields is contained in *Section 14 Appendix on page 46*.

# 9.2 OEM Keys/Secure Assets

## 9.2.1 Asymmetric Root of Trust

The Apollo4 SecureSPOT requires the OEM to generate a key pair which in turn is used to generate the OEM portion (128-bits) of the SoC Root-of-Trust. This key pair is only known to the customer, not Ambiq and ensures that the customer has complete and final control over their own SoC security. Ambiq provides tools which accept the public key from the key pair and generate a truncated hash which is stored in OTP.

Table 9-1: Asymmetric Root of Trust Field Descriptions

| Field Name | Description                                                           |

|------------|-----------------------------------------------------------------------|

| OTP_ROT4-7 | This field is the 128 bit OEM component of Root of Trust Words (HBK1) |

## 9.2.2 Symmetric Keys

The Apollo4 SecureSPOT requires two symmetric keys to be provisioned into OTP. The first key KCP is a 128-bit root key designed to authenticate the OEM provisioning tool to the Apollo4 SoC. The second symmetric key KCE is another 128-bit root key designed to be used for OEM firmware image decryption. These keys cannot be read after the OEM provisions the device in DM LCS. They can be loaded into AES hardware engine directly for symmetric key crypto operations.

Table 9-2: Symmetric Keys Field Descriptions

| Field Name | Description                                                |

|------------|------------------------------------------------------------|

| OTP_KCP0-3 | 128 bit AES Key (referred to as Provisioning Key – KCP)    |

| OTP_KCE0-3 | 128 bit AES Key (referred to as Code Encryption Key – KCE) |

## 9.2.3 Custom Key Storage

In addition to the required secure assets, the Apollo4 provides additional key storage area (1KBytes) that can be used to store any OEM specific secrets. The areas are divided into four quadrants. The access policy for each quadrant is individually controlled by the customer. The customer can manage access to each quadrant by Ambiq's Secure Bootloader (SBL). The customer can also manage access through a designated Keybank Access Key, which is programmed during provisioning. Quadrants 0 and 1 are reserved for static keys programmed as part of DM provisioning. Quadrants 2 and 3 either be used for static keys or may be optionally used for one-time programmable (OTP) run time generated keys.

Table 9-3: Custom Key Storage Field Descriptions

| Field Name                         | Description                 |

|------------------------------------|-----------------------------|

| OTP_KEYBANK_CUST_QUADRANT0_KEY0-63 | Customer Keybank Quadrant 0 |

| OTP_KEYBANK_CUST_QUADRANT1_KEY0-63 | Customer Keybank Quadrant 1 |

| OTP_KEYBANK_CUST_QUADRANT2_KEY0-63 | Customer Keybank Quadrant 2 |

| OTP_KEYBANK_CUST_QUADRANT3_KEY0-63 | Customer Keybank Quadrant 3 |

See Section 14 Appendix on page 46 for more information about the OEM Key Storage area.

# 9.3 **OEM Security Policy**

This section described the various settings that customers can use to establish a customized security policy that meets their product needs. Some of the settings are in INFO0 space while others are in OTP. Some of the fields are triple bit encoded to make electrical attacks more difficult. See *Section 14 Appendix on page 46* for more information about these fields.

# 9.3.1 Configuration of Secure Boot

Table 9-4: Secure Boot Field Descriptions

| Field Name                      | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTP_SECURITY: CUST_SECBOOT      | This field determines if Secure Boot mode is enabled. Note that this is distinct from the SE LCS state, which is a lifecycle state. Devices in DM as well as SE LCS could be configured for non-secure boot, or secureboot based on this configuration. Secureboot enabled devices go through a certificate chain based verification for the image by Ambiq SBL. |

| OTP_SECURITY: CUST_SECBOOTONRST | This field should only be used if Secure Boot (CUST_SECBOOT) is enabled. This field determines is the Secure Bootloader will execute the entire secure boot flow on every reset event. Selection of this options necessarily causes additional latency on resets.                                                                                                |

# 9.3.2 Secondary Bootloader Configuration

Table 9-5: Secondary Bootloader Field Description

| Field Name              | Description                                                                                                                                                                                                                                                                           |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTP_SECURITY : PLONEXIT | If configured to not lock it (value 0), the Secure Bootloader (SBL) keeps PROTLOCK open for customer secondary bootloader. This allows access to customer keybank area, if configured. In addition, PROTLOCK is used to deny/allow writing to the "Flash" (NVM) protection registers. |

|                         | OTP_SECURITY:PLONEXIT should be set, if no customer secondary bootloader present. This ensures that the main images do not have the ability to change NVM protection. Moreover, it also locks the OTP keybank from general access once SBL exits.                                     |

|                         | When a secondary bootloader is present (OTP_SECURITY:PLONEXIT is 0), the secondary Bootloader should assert the PROTLOCK upon exit:                                                                                                                                                   |

|                         | MCUCTRL->BOOTLOADER_b.PROTLOCK (write 1 to clear)                                                                                                                                                                                                                                     |

|                         | It is recommended to be done by Secondary Bootloader on exit, but may be optionally kept open if the entire customer application is trusted.                                                                                                                                          |

# 9.3.3 INFO Space Protections

Table 9-6: INFO Space Protections Field Description

| Field Name                       | Description                                                                                                            |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------|

| OTP_SECURITY: DIS_CUST_INFO_PROG | This field allows the customer to selectively disable write access to any or all of the four quadrants of INFO0 space. |

## 9.3.4 Update Configuration

Table 9-7: Update Configuration Field Description

| Field Name                 | Description                                                                                                                           |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| OTP_SEC_POL : AUTH_ENF_ECC | This field forces authentication of customer updates even if there is an Embedded Content Certificate (ECC) included with the update. |

| OTP_SEC_POL : ENC_ENFORCE  | This field determines whether decryption is required for all image updates.                                                           |

| OTP_SEC_POL : AUTH_ENFORCE | This field determines whether authentication is required for all image updates.                                                       |

# 9.3.5 Wired Interface Configuration

Table 9-8: Wired Interface Configuration Field Description

| Field Name                                                            | Description                                                                                                                                                                                      |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTP_BOOT_OVERRIDE : GPIO                                              | This field sets the GPIO pin to allow an external device to override the secure boot flow and force processing of a wired update.                                                                |

| OTP_BOOT_OVERRIDE : POL                                               | This field sets the polarity of the GPIO override pin as active high or low.                                                                                                                     |

| OTP_BOOT_OVERRIDE : ENABLE                                            | This field enables the GPIO override feature. By default it is disabled.                                                                                                                         |

| OTP_WIRED_CONFIG : UART OTP_WIRED_CONFIG : SPI OTP_WIRED_CONFIG : I2C | These fields enable UART, SPI, or I <sup>2</sup> C interfaces for wired update operation. The customer may enable one or more of these interfaces as needed, but typically will choose only one. |

| OTP_WIRED_CONFIG: SLAVEINTPIN                                         | This field selects the GPIO to be used by an external device to interrupt the IOS if SPI or I <sup>2</sup> C modes are enabled.                                                                  |

| OTP_WIRED_CONFIG: I2CADDR                                             | This field selects the $I^2C$ address to be used by the IOS if $I^2C$ mode is enabled.                                                                                                           |

| OTP_WIRED_CONFIG : UARTMODULE                                         | This field selects the UART instance/module (0-3) to be used for the wired interface if UART mode is enabled. Specific UART configurations are controlled through INFO0.                         |

## 9.3.6 NVM Access Protection

The NVM space for the Apollo4 is 2MB. For each of the protection fields in OTP there are four (4) 32-bit words or 128 bits total assigned to protect regions/sections of NVM. This means that the customer may protect memory blocks of 16K each. Bit 0 is the first 16K block (addresses 0x000000000 – 0x00003FFF) and Bit 127 is the last 16K block (addresses 0x001FC000 to 0x001FFFFF).

Table 9-9: NVM Access Protection Field Description

| Field Name                       | Description                                                                                                                                                                                                                                                                                           |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OTP_CUST_WPROT<br>OTP_CUST_RPROT | These fields are controlled by the customer during provisioning. They provide per manent write and read protection. WPROT provide write protection to the specific NVM 16K blocks (e.g., "Chunks"). RPROT provide "copy" or read protection. See Section 14 Appendix on page 46 for more information. |  |

|                                  | Note that protection for lower 96K of the NVM memory must never be enabled (e.g., do not set lower 6 bits (bit0-bit5) of OTP_CUST_WPROT0 or OTP_CUST_R-PROT0) as it would interfere with the functioning of the pre-installed bootloader.                                                             |  |

| OTP_SBL_WPROT<br>OTP_SBL_RPROT   | Similar to CUST_*PROT. However, while protected from general access, write/access to these NVM blocks is possible through SBL via a secure update.                                                                                                                                                    |  |

# 9.3.7 Symmetric Keybank Protections

Table 9-10: Symmetric Keybank Protection Field Description

| Field Name                              | Description                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OTP_CUSTOTP_PROGLOCK OTP_CUSTOTP_RDLOCK | These values determine the read/program access to the four quadrants of OEM/customer key banks in OTP. Quadrants #0 and #1 cannot be programmed after exiting the DM LCS until returning to the RMA LCS (and hence used for static keys), Quadrants #2 and #3 can be programmed from the main application or locked down. These can be optionally used to store run-time generated keys. |  |

|                                         | <ul> <li>RDLOCK[3:0] locks down read access to the OEM/customer key banks<br/>when running boot operations (e.g., SBR, SBL, and Secondary Boot-<br/>loader).</li> </ul>                                                                                                                                                                                                                  |  |

|                                         | RDLOCK[7:4] locks down read access to the OEM/customer READ key<br>banks after boot.                                                                                                                                                                                                                                                                                                     |  |

|                                         | If not locked, the key banks could be accessed by an authorized soft-<br>ware, as long as it has access to a 128-bit unlock key, as programmed<br>in OTP_CUSTOTP_READ_KEY <sup>1</sup>                                                                                                                                                                                                   |  |

|                                         | <ul> <li>PROGLOCK[1:0] lock down access to programming OEM/customer key<br/>banks (Quadrant #2 and #3) when running the boot operations.</li> </ul>                                                                                                                                                                                                                                      |  |

|                                         | <ul> <li>PROGLOCK[3:2] lock down access to programming OEM/customer key<br/>banks (Quadrant #2 and #3) after boot.</li> </ul>                                                                                                                                                                                                                                                            |  |

|                                         | If not locked, these key banks can be programmed by an authorized<br>software, as long as it has access to a 128-bit program key, as pro-<br>grammed in OTP_CUSTOTP_PROG_KEY <sup>1</sup>                                                                                                                                                                                                |  |

Implies multiple registers (OTP\_CUSTOTP\_PROG\_KEY0 to OTP\_CUSTOTP\_PROG\_KEY3).

Table 9-11: LCS Conditions and Results

| LCS        | Condition                                                                                 | Result                                                                 |

|------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| CM, DM, SE | (OTP_CUST_RDLOCK[0] == 0) AND<br>((SBRLOCK == 1) OR (SBLLOCK == 1) OR<br>(PROTLOCK == 1)) | Quadrant #0 Key Bank can be read during boot.                          |

| CM, DM, SE | (OTP_CUST_RDLOCK[4] == 0) AND<br>(OTP_CUSTOTP_READ_KEY0!= 0)                              | Quadrant #0 Key Bank can be read after boot using the master read key. |

| DM, RMA    | N/A                                                                                       | Quadrant #0 Key Bank can be programmed.                                |

Table 9-11: LCS Conditions and Results (Continued)

| LCS        | Condition                                                | Result                                       |

|------------|----------------------------------------------------------|----------------------------------------------|

| CM, DM, SE | (OTP_CUST_RDLOCK[1] == 0) AND                            | Quadrant #1 Key Bank can be read during      |

|            | ((SBRLOCK == 1) OR (SBLLOCK == 1) OR (PROTLOCK == 1))    | boot.                                        |

| CM, DM, SE | (OTP_CUST_RDLOCK[5] == 0) AND                            | Quadrant #1 Key Bank can be read after boot  |

|            | (OTP_CUSTOTP_READ_KEY0 != 0)                             | using the master read key.                   |

| DM, RMA    | N/A                                                      | Quadrant #1 Key Bank can be programmed       |

| CM, DM, SE | (OTP_CUST_RDLOCK[2] == 0) AND                            | Quadrant #2 Key Bank can be read during      |

|            | ((SBRLOCK == 1) OR (SBLLOCK == 1) OR (PROTLOCK == 1))    | boot.                                        |

| CM, DM, SE | (OTP_CUST_RDLOCK[6] == 0) AND                            | Quadrant #2 Key Bank can be read after boot  |

|            | (OTP_CUSTOTP_READ_KEY0 != 0)                             | using the master read key.                   |

| DM, RMA    | (OTP_CUST_PROGLOCK[0] == 0) AND                          | Quadrant #2 Key Bank can be programmed       |

|            | ((SBRLOCK == 1) OR (SBLLOCK == 1) OR<br>(PROTLOCK == 1)) | during boot.                                 |

| DM, RMA    | (OTP_CUST_PROGLOCK[2] == 0) AND                          | Quadrant #2 Key Bank can be programmed       |

|            | (OTP_CUSTOTP_PROG_KEY !=0)                               | after boot using the master programming key. |

| CM, DM, SE | (OTP_CUST_RDLOCK[3] == 0) AND                            | Quadrant #3 Key Bank can be read during      |

|            | ((SBRLOCK == 1) OR (SBLLOCK == 1) OR (PROTLOCK == 1))    | boot.                                        |

| CM, DM, SE | (OTP_CUST_RDLOCK[7] == 0) AND                            | Quadrant #3 Key Bank can be read after boot  |

|            | (OTP_CUSTOTP_READ_KEY0 != 0)                             | using the master read key.                   |

| DM, RMA    | (OTP_CUST_PROGLOCK[1] == 0) AND                          | Quadrant #3 Key Bank can be programmed       |

|            | ((SBRLOCK == 1) OR (SBLLOCK == 1) OR (PROTLOCK == 1))    | during boot.                                 |

| DM, RMA    | (OTP_CUST_PROGLOCK[3] == 0) AND                          | Quadrant #3 Key Bank can be programmed       |

|            | (OTP_CUSTOTP_PROG_KEY !=0)                               | after boot using the master programming key. |

**NOTE:** The expression ((SBRLOCK == 1) OR (SBLLOCK == 1) OR (PROTLOCK == 1) implies that the code is running in the Bootloader and not yet reached the main application.

## 9.3.8 Debug Control

The Apollo4 SoC supports fine granularity debug control through a hardware Debug Control Unit (DCU). There are distinct debug features which are controlled by individual DCU bits. As can be seen in *Section 14 Appendix on page 46*, debug control defaults differ based on the LCS.

Hardware raw DCU bits are triple encoded: b'101 enables a feature, while b'010 disables it.

Table 9-12: Debug Control Field Description

| Field Name              | Description                                                                                                                                                                                                                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTP_LOCKMASK[0-3]       | The DCU values can be locked and prevented from further modifications by configuring and specifying the triple bits corresponding to the feature to be locked.                                                                                                                                          |

| OTP_DCU_DISABLEOVERRIDE | This field provides the ability to disable a feature upon SBL exit, even if the DCU settings allow for the feature. Setting a bit in the 21-bit field forces the desired debug feature to be disabled. Unlike the DCU locking, this override can be reversed by programming MCUCTRL->DEBUGGER register. |

# 9.4 OEM Infospace (INFO0) Configuration

INFO0 provides MRAM based NVM storage which is separate from the main MRAM. Some of the fields in INFO0 are predefined for certain configurations and settings to further modulate the security settings in the OTP. It also contains fields which allow customers to override the defaults for certain attributes of the boot flow.

Rest of the INFO0 (undefined) is free for customers to use to store any other device information.