## **QUICK START GUIDE**

# **Apollo4 EVB**

(EVB Revision 3)

Ultra-low Power Apollo SoC Family

Doc. ID: QS-A4-4p2

Document Revision 4.2, December 2025

## **Legal Information and Disclaimers**

AMBIQ MICRO INTENDS FOR THE CONTENT CONTAINED IN THE DOCUMENT TO BE ACCURATE AND RELIABLE. THIS CONTENT MAY, HOWEVER, CONTAIN TECHNICAL INACCURACIES, TYPOGRAPHICAL ERRORS OR OTHER MISTAKES. AMBIQ MICRO MAY MAKE CORRECTIONS OR OTHER CHANGES TO THIS CONTENT AT ANY TIME. AMBIQ MICRO AND ITS SUPPLIERS RESERVE THE RIGHT TO MAKE CORRECTIONS, MODIFICATIONS, ENHANCEMENTS, IMPROVEMENTS AND OTHER CHANGES TO ITS PRODUCTS, PROGRAMS AND SERVICES AT ANY TIME OR TO DISCONTINUE ANY PRODUCTS, PROGRAMS, OR SERVICES WITHOUT NOTICE.

THE CONTENT IN THIS DOCUMENT IS PROVIDED "AS IS". AMBIQ MICRO AND ITS RESPECTIVE SUPPLIERS MAKE NO REPRESENTATIONS ABOUT THE SUITABILITY OF THIS CONTENT FOR ANY PURPOSE AND DISCLAIM ALL WARRANTIES AND CONDITIONS WITH REGARD TO THIS CONTENT, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHT.

AMBIQ MICRO DOES NOT WARRANT OR REPRESENT THAT ANY LICENSE, EITHER EXPRESS OR IMPLIED, IS GRANTED UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT OF AMBIQ MICRO COVERING OR RELATING TO THIS CONTENT OR ANY COMBINATION, MACHINE, OR PROCESS TO WHICH THIS CONTENT RELATE OR WITH WHICH THIS CONTENT MAY BE USED.

USE OF THE INFORMATION IN THIS DOCUMENT MAY REQUIRE A LICENSE FROM A THIRD PARTY UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF THAT THIRD PARTY, OR A LICENSE FROM AMBIQ MICRO UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF AMBIQ MICRO.

INFORMATION IN THIS DOCUMENT IS PROVIDED SOLELY TO ENABLE SYSTEM AND SOFTWARE IMPLE-MENTERS TO USE AMBIQ MICRO PRODUCTS. THERE ARE NO EXPRESS OR IMPLIED COPYRIGHT LICENSES GRANTED HEREUNDER TO DESIGN OR FABRICATE ANY INTEGRATED CIRCUITS OR INTE-GRATED CIRCUITS BASED ON THE INFORMATION IN THIS DOCUMENT. AMBIQ MICRO RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN. AMBIQ MICRO MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR DOES AMBIQ MICRO ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT, AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABIL-ITY, INCLUDING WITHOUT LIMITATION CONSEQUENTIAL OR INCIDENTAL DAMAGES. "TYPICAL" PARAME-TERS WHICH MAY BE PROVIDED IN AMBIQ MICRO DATA SHEETS AND/OR SPECIFICATIONS CAN AND DO VARY IN DIFFERENT APPLICATIONS AND ACTUAL PERFORMANCE MAY VARY OVER TIME. ALL OPERATING PARAMETERS, INCLUDING "TYPICALS" MUST BE VALIDATED FOR EACH CUSTOMER APPLICATION BY CUS-TOMER'S TECHNICAL EXPERTS. AMBIQ MICRO DOES NOT CONVEY ANY LICENSE UNDER NEITHER ITS PAT-ENT RIGHTS NOR THE RIGHTS OF OTHERS. AMBIQ MICRO PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN SYSTEMS INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR OTHER APPLICATIONS INTENDED TO SUPPORT OR SUSTAIN LIFE, OR FOR ANY OTHER APPLICA-TION IN WHICH THE FAILURE OF THE AMBIQ MICRO PRODUCT COULD CREATE A SITUATION WHERE PER-SONAL INJURY OR DEATH MAY OCCUR. SHOULD BUYER PURCHASE OR USE AMBIQ MICRO PRODUCTS FOR ANY SUCH UNINTENDED OR UNAUTHORIZED APPLICATION, BUYER SHALL INDEMNIFY AND HOLD AMBIQ MICRO AND ITS OFFICERS, EMPLOYEES, SUBSIDIARIES, AFFILIATES, AND DISTRIBUTORS HARM-LESS AGAINST ALL CLAIMS, COSTS, DAMAGES, AND EXPENSES, AND REASONABLE ATTORNEY FEES ARIS-ING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PERSONAL INJURY OR DEATH ASSOCIATED WITH SUCH UNINTENDED OR UNAUTHORIZED USE, EVEN IF SUCH CLAIM ALLEGES THAT AMBIQ MICRO WAS NEGLIGENT REGARDING THE DESIGN OR MANUFACTURE OF THE PART.

## **Table of Content**

| 1. Introduction                               | 6  |

|-----------------------------------------------|----|

| 2. Document Revision History                  | 6  |

| 3. Reference Documents and Software           |    |

| 4. Quick Start                                | 7  |

| 5. Overview of the Apollo4 EVB                | 8  |

| 6. Debug Interface                            | 11 |

| 7. Software Development Tools                 | 13 |

| 8. Power Supply Options and Measuring Current | 14 |

| 9. Non-Power Solder Bridges                   | 18 |

| 10. Ordering Information                      | 20 |

All rights reserved.

# **List of Figures**

| Figure 1. Apollo4 EVB Revision 3                                     | 8  |

|----------------------------------------------------------------------|----|

| Figure 2. Apollo4 EVB - Major Components                             | 8  |

| Figure 3. Apollo4 EVB - Top-side Parts Location                      | 9  |

| Figure 4. Apollo4 EVB - Bottom-side Parts Location                   | 9  |

| Figure 5. Apollo4 EVB Using On-board J-Link Debugger                 | 11 |

| Figure 6. Apollo4 EVB's DEBUG IN Header (J13)                        | 12 |

| Figure 7. Apollo4 Power Supplies Solder Bridge Connection            | 14 |

| Figure 8. Apollo4 EVB USB Load Switch Circuit                        | 15 |

| Figure 9. Apollo4 EVB VDD18/MIPI Load Switch Circuit                 | 15 |

| Figure 10. Apollo4 EVB Voltage Test Points on Header J2              | 16 |

| Figure 11. Apollo4 EVB, Rev. 1 and 2, Voltage Selection on Header J3 | 16 |

| Figure 12. Apollo4 EVB, Rev. 3, Voltage Selection on Header J3       | 16 |

| Figure 13. Audio Jack J18 and AUDADC Audio Source Selections         | 19 |

| Figure 14. Audio Header J17                                          | 19 |

## **List of Tables**

| Table 1: Document Revision History                        | 6  |

|-----------------------------------------------------------|----|

| Table 2: Peripherals Supporting Solder Bridge Connections |    |

| Table 3: EVB Ordering Information                         | 20 |

| Table 4: SoC Ordering Information                         |    |

## 1. Introduction

This document provides guidance for setting up the Apollo4 Evaluation Board (EVB), revision 3, part number AMAP4EVB, to get started executing code examples, measuring power consumption in various configurations, and beginning software development.

This version of the EVB contains silicon version B2 of the Apollo4 SoC.

## 2. Document Revision History

| Rev# | Date     | Description                                                                                                                                                |  |  |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3.0  | Jul 2021 | Initial release for EVB revision 3                                                                                                                         |  |  |

| 4.0  | Aug 2021 | Updates: - Reference Documents and Software section added - Quick Start section added - Parts Location drawings added - Ordering Information section added |  |  |

| 4.1  | Mar 2023 | Updated section "Software Development Tools" on page 13                                                                                                    |  |  |

| 4.2  | Dec 2025 | Added important note about installing the Segger J-Link software in Software Development Tools section.                                                    |  |  |

**Table 1: Document Revision History**

### 3. Reference Documents and Software

The following items, which can be downloaded from the Apollo4 Product Page link on https://ambiq.com/, may be useful in understanding and using the EVB.

- EVB Schematic

- Apollo4 Datasheet

- Apollo4 Family Programmer's Guide

- Apollo4/Apollo4 Blue Errata List

- AmbiqSuite SDK

#### 4. Quick Start

The EVB Kit comes with the following items:

- Apollo4 Evaluation Board (EVB)revision 3

- USB Type C cable

- Four adhesive-backed rubber feet

- Extra jumpers

**Caution:** The EVB has components loaded on the back of the board. Care should be taken to not damage these components. The included rubber feet should be applied to the bottom of the board to prevent direct contact between the components and a desk surface.

The EVB comes with jumpers pre-configured for default operation. Also, it has been pre-programmed with the Binary Counter example program. To start EVB program execution, connect the USB-C cable from a USB port on a PC to the J-Link USB connector (J6) on the EVB, and turn on the power switch (SW4). The blue LED under the power switch should illuminate.

Monitor the three LEDs on the bottom of the EVB (D3-D5). The LEDs should light in a binary count-up pattern, and repeat.

The AmbiqSuite SDK provides many example programs that may be run on the EVB. To run these examples, download the SDK via the link provided above and select any of the pre-built examples in the SDK at /boards/apollo4b\_bga\_evb/examples.

## 5. Overview of the Apollo4 EVB

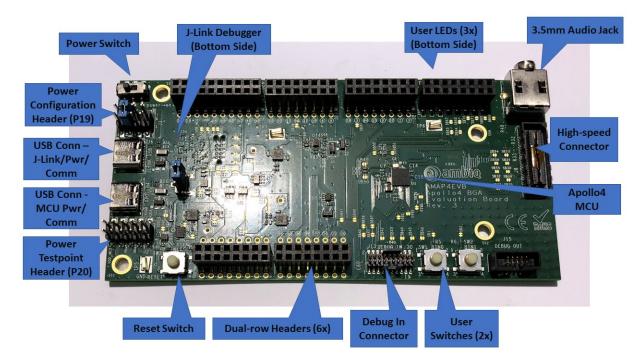

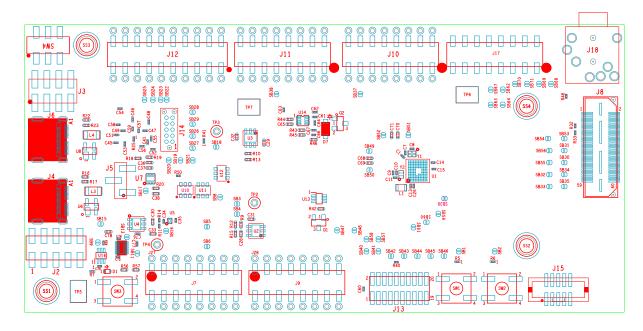

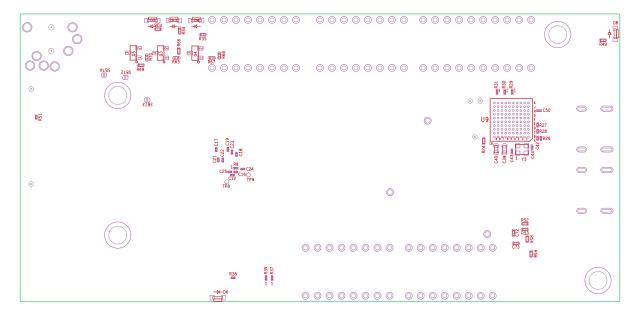

The Apollo4 EVB, version 3, features signal-accessible headers and an integrated J-Link debugger. The following figures show the board layout, its major features and the location of all components.

Figure 1. Apollo4 EVB Revision 3

Figure 2. Apollo4 EVB - Major Components

Figure 3. Apollo4 EVB - Top-side Parts Location

Figure 4. Apollo4 EVB - Bottom-side Parts Location

#### The EVB has these features:

- Apollo4 SoC in the BGA package (AMAP42KK-KCR-B2)

- Low power reference design

- Multiple power/clock options

- USB Type C connector for power/download/debug

- USB Type C connector for power/data to Apollo4

- Segger J-Link debugger

- Debugger-in port (J13) (SWD or ETM)

- Three user-controlled LEDs

- Two push buttons for application use, plus a reset push button

- Power slide switch with LED power indicator

- Five headers (J7, J9-J12) for pin/power access to a shield board

- Test points for power measurements

- High-speed connector (J8 QSH-030-01-L-D-A) for interfacing to displays and/or high-speed memory

- RF switch/connector (Murata MM8430-2610RA1) for BLE PHY testing

- Multiple solder-bridge options for power supply flexibility and peripheral access options

- 3.5 mm audio jack (SJ-435107) for evaluating low-power analog audio interface

- RoHS compliant

**CAUTION:** The EVB has components loaded on the back of the board. Care should be taken to not damage these components.

#### 5.1 Secure Boot on the Apollo4 SoC

Apollo4 SoC parts from the Ambiq factory are preprogrammed with a Secure Bootloader and an uninitialized Customer Info Space, referred to as INFO0. Initial provisioning of the part would include programming a valid INFO0 and programming the main firmware image in the flash. The Apollo4 EVB is shipped with the INFO0 configuration pre-programmed with optimal settings for the EVB layout:

- Default boot to non-secure mode

- 2. Enable Boot Override to Push Button on GPIO18 (OTP setting) BTN0/SW1.

- 3. Enable Boot Override by wiring GPIO18 (OTP Setting) to the Push Button on GPIO17 and pressing BTN0/SW1.

- 4. Enable wired updates over UART0

- A. UART0 is mapped to J-Link (OTP Setting).

- B. Baud rate is 115200 bps, no-parity, 8-bit data length, no flow control.

- C. Timeout is 3 seconds.

For reference, the following settings are programmed into INFO0 on the Apollo4 SoC resident on the EVB:

- SIMO Buck is NOT enabled.

- Secure Bootloader (SBL) interface is configured to UART using GPIO47 and GPIO60, which allows secure boot to be performed over the J-Link COM interface of the EVB.

- SBL override pin is configured to GPIO18 which is BTN0/SW1 on the EVB.

- All Flash and Debugger protection features are disabled.

For information on changing the INFO0 settings as well as using the Secure Bootloader, please refer to the *README.txt* file, which can be found in the tools\apollo4b\_scripts folder of the latest SDK release supporting the Apollo4 family. This folder contains a number of python scripts to demonstrate generation of INFO0 settings, customer main images, and the creation of images for the Wired Update protocol over UART.

## 6. Debug Interface

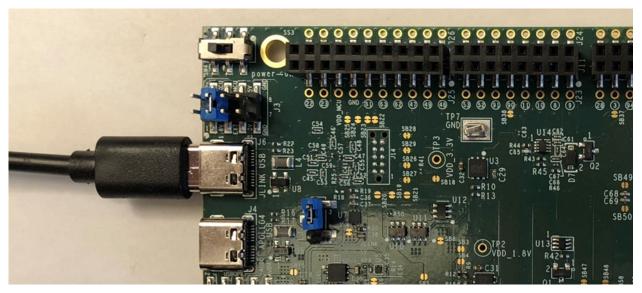

Figure 5 shows the Apollo4 EVB set up for standard debug using the on-board J-Link debugger and on-board power supply.

Figure 5. Apollo4 EVB Using On-board J-Link Debugger

The debug interface is supported by standard J-Link drivers from Segger. Please refer to "Software Development Tools" on page 13 for more details on J-Link debug support.

## 6.1 Use of External Debugger

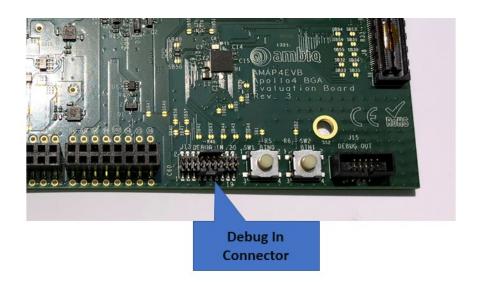

This EVB also supports the use of an external Cortex SWD debug interface through a 20-pin debug header (DEBUG IN - J13) as shown in Figure 6. See the EVB schematic for connector pinout.

Figure 6. Apollo4 EVB's DEBUG IN Header (J13)

No jumper changes are required to use an external debug adapter. Simply connect the external debug adapter with a ribbon cable connector to the "DEBUG IN" header.

NOTE: Remove protective guard before attempting to connect to the DEBUG IN header.

## 7. Software Development Tools

The standard Segger J-Link debug interface is used on the Apollo4 EVB. Please install the latest Segger J-Link software, and configure your preferred development IDE (Keil, IAR, or Eclipse) to use the J-Link debug interface. Please consult the release notes of the latest/applicable SDK release for the version of the tools used during testing of the SDK and which are recommended for development with the SDK.

Links to the supported development tools are listed below.

- SEGGER J-Link Software: <a href="https://www.segger.com/downloads/jlink">https://www.segger.com/downloads/jlink</a>

- KEIL uVision 5 (ARM Compiler 5): <a href="https://www.keil.com/demo/eval/arm.htm">https://www.keil.com/demo/eval/arm.htm</a>

- Latest Keil Pack (CMSIS Ambig Pack): http://www.keil.com/dd2/pack/#/third-party-download-dialog

- IAR IDE/Compiler: https://www.iar.com/iar-embedded-workbench/tools-for-arm/arm-cortex-m-edition/

- GCC (GNU Arm Embedded Toolchain): <a href="https://gcc.gnu.org">https://gcc.gnu.org</a>

Regardless of IDE used, please install the Segger J-Link software. All of the above development environments support J-Link, but you must have the latest J-Link software installed. Most alternate development environments also support J-Link.

Please refer to the AmbiqSuite SDK Getting Started Guide for more details on setting up development IDEs to use J-Link.

#### **IMPORTANT NOTE**

When installing the Segger J-Link software described above, it may be necessary to select the "Install Legacy USB Driver" option in order to properly enable the USB connection. This option is not selected by default in the Segger installation setup dialog box, so the checkbox has to be checked to install the legacy USB driver. (This is the only default installation option that needs to be changed when installing the software.)

#### 8. **Power Supply Options and Measuring Current**

The Apollo4 EVB is intended to operate off of a 5 V supply, which is used to generate downstream voltages.

There are two power supply options for the EVB SoC:

- Operate at 1.9 V by default as provided by the on-board power supply (referred to as nominal "VDD 1.8V"). This can be adjusted to 1.8 V by shorting SB4 shown on the Power Supplies page of the EVB schematic<sup>(1)</sup>.

- Provide externally supplied power.

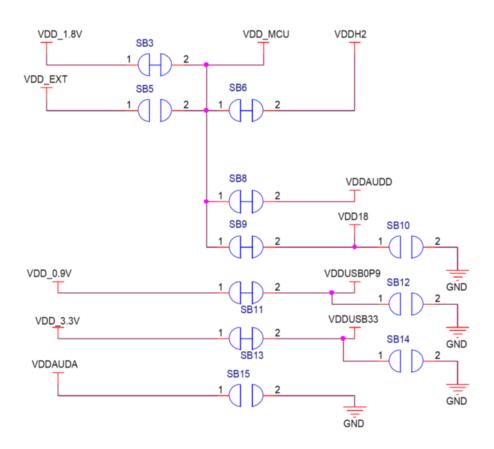

The EVB utilizes solder-bridges for connecting and disconnecting rails from power supplies, whether generated on-board or off-board. Figure 7 shows the solder-bridge connection strategy between various on-board power supplies and the SoC's power rails.

Figure 7. Apollo4 Power Supplies Solder Bridge Connection

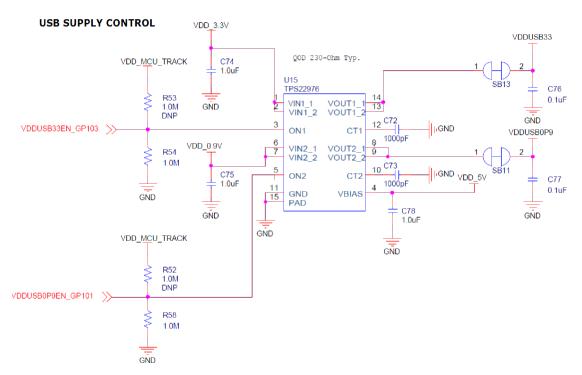

Figure 8 shows the USB load switch circuit producing the voltage supplied to VDDUSB33 and VDDUSB0 9 through solder-bridges SB13 and SB11, respectively. These solder bridges are shorted by default.

Page 14

<sup>1.</sup> Refer to the EVB schematic and assembly drawing for purpose and location of all solder bridges on the EVB.

Figure 8. Apollo4 EVB USB Load Switch Circuit

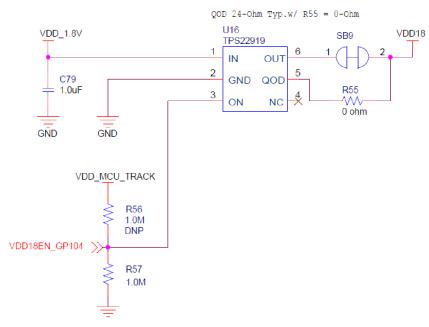

Similarly, Figure 9 shows the load switch circuit producing the voltage supplied to the MIPI DPHY VDD18 supply through solder-bridge SB9. This solder bridge is also shorted by default.

Figure 9. Apollo4 EVB VDD18/MIPI Load Switch Circuit

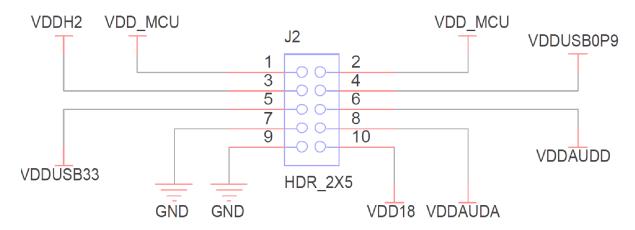

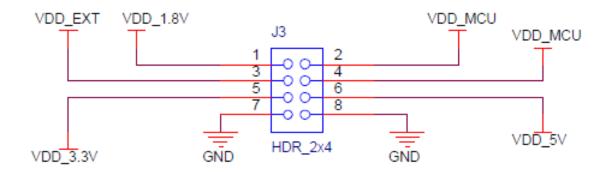

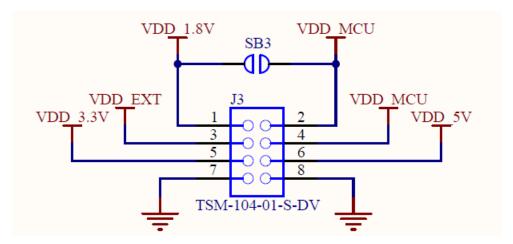

As shown in the following figures, headers J2 and J3 provide easy access to the various system and chiplevel power supplies present on the EVB. These can be used in conjunction with the above solder-bridges to measure current, monitor voltage, or provide externally generated power to each specific rail.

Figure 10. Apollo4 EVB Voltage Test Points on Header J2

Figure 11. Apollo4 EVB, Rev. 1 and 2, Voltage Selection on Header J3

Figure 12. Apollo4 EVB, Rev. 3, Voltage Selection on Header J3

### 8.1 Measuring Current

If the user wants to use a separate power supply for the EVB, then SB3 shown above should be open, and either SB5 should be shorted or pins 3 and 4 of J3 should be jumped. The external power rail can be applied to VDD\_EXT on J3, pin 3. Consult the electrical specifications in the Apollo4 Datasheet for the acceptable operating range for VDD\_MCU.

Note: The J-Link I/O voltage should be set to the new VDD\_IO of the chip, and therefore SB19 (not shown in Figure 7) should be opened and SB20 should be shorted (soldered).

Use of the EVB using the on-board SoC supply may be restored by disconnecting the external supply (if connected) and either shorting SB3 or jumping between pins 1 and 2 of J3. The J-Link I/O voltage also should be restored.

## 9. Non-Power Solder Bridges

#### 9.1 Solder Bridges for Reducing Trace Length to Optimize Performance

The following peripherals support solder-bridge connections, which allow for optimized performance by reducing overall trace length at the cost of losing connectivity to their respective GPIO headers. Note that these connections can be reset by applying solder across the solder-bridge.

| Peripheral                          | GPIO                        | Description                                                                                                                                                                      |  |  |

|-------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Display Controller, MSPI0 37, 64-73 |                             | Opening the following corresponding solder-bridges shown in Figure 3 connects these GPIO exclusively to J8, with minimal trace stubs: SB36, SB56, SB55, SB30 - SB35, SB53, SB54. |  |  |

| ЕТМ                                 | 50-54, 55 (open by default) | Opening the following corresponding solder-bridges shown in Figure 3 connect these GPIO exclusively to J13: SB42 - SB46, SB57. SWO is default connection to J13.                 |  |  |

**Table 2: Peripherals Supporting Solder Bridge Connections**

Additionally, the LED indicators can be disconnected from GPIO30, GPIO60 and GPIO90 by opening their respective solder-bridges (SB37, SB38, and SB39). GPIO47, GPIO58, GPIO59 and GPIO60 are used for UART communication with the on-board J-Link. Opening SB26-SB29 frees these pins for exclusive use with the standard GPIO headers J10 and J12.

### 9.2 Solder Bridges for Audio Selectivity

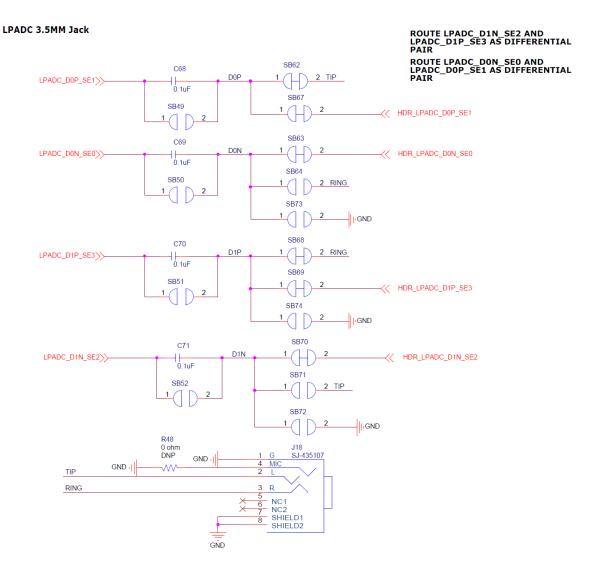

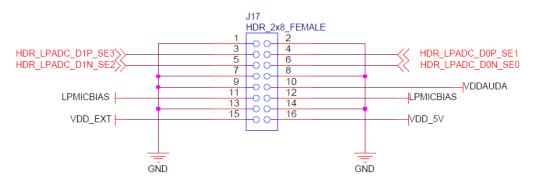

As shown in Figure 13, a single audio jack, J18, provides stereo audio input routed to AUDADC (also referred to as LPADC) inputs on the SoC. Alternatively, up to 4 single-ended or 2 differential pair audio signals as shown in Figure can be input on connector J17 which is routed on the EVB as differential pair(s) to AUDADC inputs. The default (shorted) solder bridge configuration enables either of these input options.

Figure 13. Audio Jack J18 and AUDADC Audio Source Selections

Figure 14. Audio Header J17

# 10. Ordering Information

| Device Name | Orderable<br>Part Number | EVB<br>Revision | SoC     | SoC SoC Package |             |

|-------------|--------------------------|-----------------|---------|-----------------|-------------|

| Apollo4 EVB | AMAP4EVB                 | 3               | Apollo4 | 146-pin BGA     | –20 to 60°C |

**Table 3: EVB Ordering Information**

| Device Name | Orderable<br>Part Number <sup>a</sup> | MRAM | RAM    | Package     | Packing       | Temperature<br>Range |

|-------------|---------------------------------------|------|--------|-------------|---------------|----------------------|

| Apollo4 SoC | AMAP42KK-KBR-<br>B2                   | 2 MB | 1.8 MB | 146-pin BGA | Tape and Reel | –20 to 60°C          |

**Table 4: SoC Ordering Information**

a. The silicon revision is identified by the first letter in the bottom row of the package's top marking.

©2025 Ambiq Micro, Inc. All rights reserved.

Ambiq Micro, Inc.

6500 River Place Boulevard, Building 7,

Suite 200, Austin, TX 78730-1156

www.ambiq.com/

sales@ambiqmicro.com

https://support.ambiqmicro.com

+1 (512) 879-2850

QS-A4-4p2

Version 4.2

Dec 2025