# **QUICK START GUIDE**

# **Apollo510 EVB**

(EVB Revision 2.2)

Ultra-low Power Apollo SoC Family

Doc. ID: QS-A510-2p1

Document Revision 2.1, November 2025

# **Legal Information and Disclaimers**

AMBIQ MICRO INTENDS FOR THE CONTENT CONTAINED IN THE DOCUMENT TO BE ACCURATE AND RELIABLE. THIS CONTENT MAY, HOWEVER, CONTAIN TECHNICAL INACCURACIES, TYPOGRAPHICAL ERRORS OR OTHER MISTAKES. AMBIQ MICRO MAY MAKE CORRECTIONS OR OTHER CHANGES TO THIS CONTENT AT ANY TIME. AMBIQ MICRO AND ITS SUPPLIERS RESERVE THE RIGHT TO MAKE CORRECTIONS, MODIFICATIONS, ENHANCEMENTS, IMPROVEMENTS AND OTHER CHANGES TO ITS PRODUCTS, PROGRAMS AND SERVICES AT ANY TIME OR TO DISCONTINUE ANY PRODUCTS, PROGRAMS, OR SERVICES WITHOUT NOTICE.

THE CONTENT IN THIS DOCUMENT IS PROVIDED "AS IS". AMBIQ MICRO AND ITS RESPECTIVE SUPPLIERS MAKE NO REPRESENTATIONS ABOUT THE SUITABILITY OF THIS CONTENT FOR ANY PURPOSE AND DISCLAIM ALL WARRANTIES AND CONDITIONS WITH REGARD TO THIS CONTENT, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHT.

AMBIQ MICRO DOES NOT WARRANT OR REPRESENT THAT ANY LICENSE, EITHER EXPRESS OR IMPLIED, IS GRANTED UNDER ANY PATENT RIGHT, COPYRIGHT, MASK WORK RIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT OF AMBIQ MICRO COVERING OR RELATING TO THIS CONTENT OR ANY COMBINATION, MACHINE, OR PROCESS TO WHICH THIS CONTENT RELATE OR WITH WHICH THIS CONTENT MAY BE USED.

USE OF THE INFORMATION IN THIS DOCUMENT MAY REQUIRE A LICENSE FROM A THIRD PARTY UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF THAT THIRD PARTY, OR A LICENSE FROM AMBIQ MICRO UNDER THE PATENTS OR OTHER INTELLECTUAL PROPERTY OF AMBIQ MICRO.

INFORMATION IN THIS DOCUMENT IS PROVIDED SOLELY TO ENABLE SYSTEM AND SOFTWARE IMPLE-MENTERS TO USE AMBIQ MICRO PRODUCTS. THERE ARE NO EXPRESS OR IMPLIED COPYRIGHT LICENSES GRANTED HEREUNDER TO DESIGN OR FABRICATE ANY INTEGRATED CIRCUITS OR INTE-GRATED CIRCUITS BASED ON THE INFORMATION IN THIS DOCUMENT. AMBIQ MICRO RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN. AMBIQ MICRO MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR DOES AMBIQ MICRO ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT, AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABIL-ITY, INCLUDING WITHOUT LIMITATION CONSEQUENTIAL OR INCIDENTAL DAMAGES. "TYPICAL" PARAME-TERS WHICH MAY BE PROVIDED IN AMBIQ MICRO DATA SHEETS AND/OR SPECIFICATIONS CAN AND DO VARY IN DIFFERENT APPLICATIONS AND ACTUAL PERFORMANCE MAY VARY OVER TIME. ALL OPERATING PARAMETERS, INCLUDING "TYPICALS" MUST BE VALIDATED FOR EACH CUSTOMER APPLICATION BY CUS-TOMER'S TECHNICAL EXPERTS. AMBIQ MICRO DOES NOT CONVEY ANY LICENSE UNDER NEITHER ITS PAT-ENT RIGHTS NOR THE RIGHTS OF OTHERS. AMBIQ MICRO PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN SYSTEMS INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR OTHER APPLICATIONS INTENDED TO SUPPORT OR SUSTAIN LIFE, OR FOR ANY OTHER APPLICA-TION IN WHICH THE FAILURE OF THE AMBIQ MICRO PRODUCT COULD CREATE A SITUATION WHERE PER-SONAL INJURY OR DEATH MAY OCCUR. SHOULD BUYER PURCHASE OR USE AMBIQ MICRO PRODUCTS FOR ANY SUCH UNINTENDED OR UNAUTHORIZED APPLICATION, BUYER SHALL INDEMNIFY AND HOLD AMBIQ MICRO AND ITS OFFICERS, EMPLOYEES, SUBSIDIARIES, AFFILIATES, AND DISTRIBUTORS HARM-LESS AGAINST ALL CLAIMS, COSTS, DAMAGES, AND EXPENSES, AND REASONABLE ATTORNEY FEES ARIS-ING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PERSONAL INJURY OR DEATH ASSOCIATED WITH SUCH UNINTENDED OR UNAUTHORIZED USE, EVEN IF SUCH CLAIM ALLEGES THAT AMBIQ MICRO WAS NEGLIGENT REGARDING THE DESIGN OR MANUFACTURE OF THE PART.

# **Table of Content**

| 1. Introduction                                | 6  |

|------------------------------------------------|----|

| 2. Document Revision History                   | 6  |

| 3. Reference Documents and Software            |    |

| 4. Quick Start                                 | 7  |

| 5. Overview of the Apollo510 EVB               | 8  |

| 6. Secure Boot on the Apollo510 SoC            | 12 |

| 7. Header Pin Assignments                      | 13 |

| 8. Debug Interface                             | 16 |

| 9. Software Development Tools                  | 17 |

| 10. Power Supply Options and Measuring Current | 18 |

| 11. Ordering Information                       | 23 |

|                                                |    |

# **List of Figures**

| Figure 1. EVB Top View                                     | 9  |

|------------------------------------------------------------|----|

| Figure 2. EVB Bottom View                                  |    |

| Figure 3. EVB Major Components                             |    |

| Figure 4. EVB Top Side Components                          |    |

| Figure 5. EVB Bottom Side Components                       | 11 |

| Figure 6. J14/J15 MikroBUS Headers - Function Options      | 13 |

| Figure 7. J8/J9 General Purpose Headers - Function Options | 13 |

| Figure 8. J7 High-speed Header - Function Options          | 14 |

| Figure 9. Board View of J7 High-speed Header               | 15 |

| Figure 10. Using On-board J-Link Debugger                  | 16 |

| Figure 11. J2 Debug-In Header                              | 16 |

| Figure 12. J6 External Supply Header                       | 18 |

| Figure 13. J4 Power Supply Jumper Connections              | 19 |

| Figure 14. J4 Default Jumper Configuration                 | 19 |

| Figure 15. J5 Power Supply Jumper Connections              | 20 |

| Figure 16. J5 Default Jumper Configuration                 | 20 |

| Figure 17. USB Load Switch Circuit                         | 21 |

| Figure 18. VDD18/MIPI Load Switch Circuit                  | 21 |

| Figure 19. J3 Voltage Test Points Header                   | 22 |

| Figure 20. Board View of J3 Voltage Test Points Header     | 22 |

# **List of Tables**

| Table 1: Document Revision History             | 6 |

|------------------------------------------------|---|

| Table 2: J4 Default Jumper Configuration Table |   |

| Table 3: J5 Default Jumper Configuration Table |   |

| Table 4: EVB Ordering Information              |   |

| Table 5: Apollo510 SoC Ordering Information    |   |

# 1. Introduction

This document provides guidance for setting up the Apollo510 Evaluation Board (EVB), revision 2.2, part number AP510EVB, to get started executing code examples, measuring power consumption in various configurations, and beginning software development.

# 2. Document Revision History

| Rev# | Date     | Description                                                                                                                                                                                                    |  |  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0  | Jan 2025 | Document initial public release  Updated for EVB Revision 2.2                                                                                                                                                  |  |  |

| 2.0  | May 2025 |                                                                                                                                                                                                                |  |  |

| 2.1  | Nov 2025 | <ul> <li>- Added option to use the low-noise VDD1V8_LN supply to source VDD_MCU.</li> <li>- Added important note about installing the Segger J-Link software in Software Development Tools section.</li> </ul> |  |  |

**Table 1: Document Revision History**

### 3. Reference Documents and Software

The latest version of the following items, which can be acquired through your Ambiq Sales contact, may be useful in understanding and using the EVB.

- EVB Schematic

- Apollo510 Datasheet

- Apollo510/Apollo510B Errata List

- AmbiqSuite SDK

### 4. Quick Start

The EVB Kit comes with the following items:

- Apollo510 Evaluation Board (EVB), revision 2.2

- USB Type C cable

- · Four adhesive-backed rubber feet

- Extra jumpers

**Caution:** The EVB has components loaded on the back of the board. Care should be taken to not damage these components. The included rubber feet should be applied to the bottom of the board to prevent direct contact between the components and a desk surface.

The EVB comes with jumpers pre-configured for default operation. To start EVB program execution, connect the USB-C cable from a USB port on a PC to the J-Link USB connector (J16) on the EVB, and turn on the power switch (SW4). The green LED next to the power switch should illuminate.

The AmbiqSuite SDK provides many example programs that may be run on the EVB. To run these examples, download the SDK from the Ambiq Content Portal (https://contentportal.ambiq.com/login) and select any of the pre-built examples in the SDK at /boards/apollo510\_evb/examples. The examples should be programmed at address 0x410000.

# 5. Overview of the Apollo510 EVB

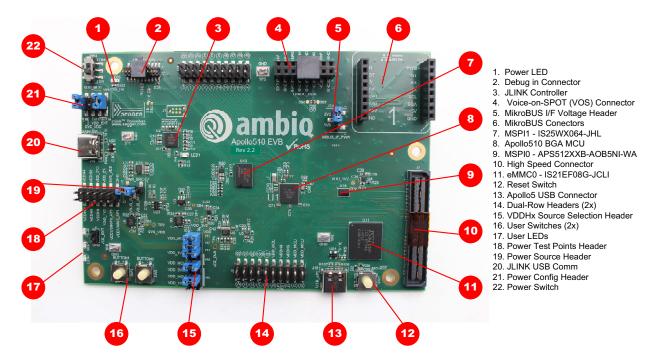

The Apollo510 EVB has the following features:

- Apollo510 Arm® Cortex®-M55 based SoC in the BGA package (AP510NFA-CBR)

- USB Type C connector for power/download/debug (J16)

- USB Type C connector for power/data to Apollo510 SoC (J18)

- On-board Segger J-Link debugger

- Debug-in port (J2) (SWD or ETM)

- Three user-controlled LEDs

- Two push buttons for application use, plus a reset push button

- Power slide switch with LED power indicator

- On-board interfaces:

- MSPI x16 (Hex) PSRAM (AP Memory APS512XXN-AOB4BI-WBRZ)

- MSPI x8 Octal Flash memory (ISSI IS25WX064-JHL)

- SDIO 8 GB eMMC (ISSI IS21EF08G-JCLI)

- High-speed expansion connector

- MikroBUS socket interface

- General purpose male headers (J8 and J9) for I/O and power access to a shield board

- Test points for voltage measurements and jumpers for current measurements

- Solder bridge options for power supply flexibility and peripheral access options

- RoHS compliant

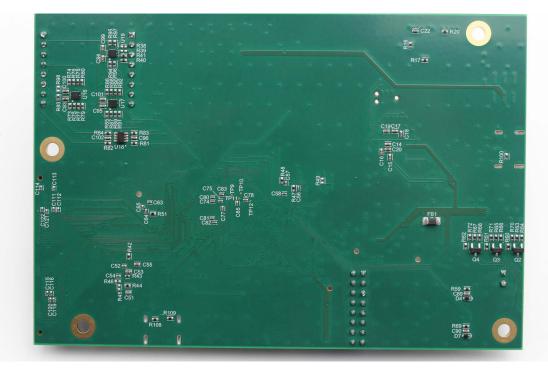

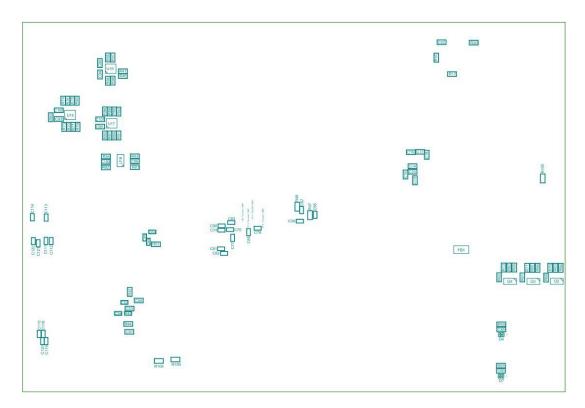

**CAUTION:** The EVB has components loaded on the back of the board. Care should be taken to not damage these components.

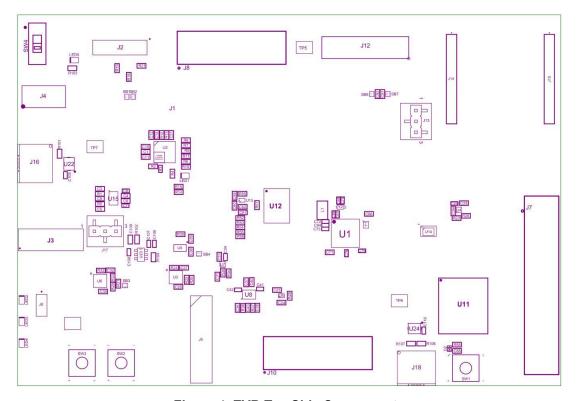

The following figures show the board layout, its major components and the location of all components.

Figure 1. EVB Top View

Figure 2. EVB Bottom View

Figure 3. EVB Major Components

Figure 4. EVB Top Side Components

Figure 5. EVB Bottom Side Components

## 6. Secure Boot on the Apollo510 SoC

The on-board Apollo510 SoC is preprogrammed with a Secure Bootloader and an uninitialized Customer Info Space, referred to as INFO0. Initial provisioning of the part would include programming a valid INFO0 and programming the main firmware image in the flash.

The Apollo510 EVB is shipped with the INFO0 configuration pre-programmed with optimal settings for the EVB layout which would include the following features/settings:

- 1. Default boot to non-secure mode

- 2. Enable Boot Override to Push Button on GPIO93 (OTP setting) BTN0 (SW2).

- 3. Enable wired updates over UART0

- A. UART0 is mapped to J-Link (OTP Setting).

- B. Baud rate is 115200 bps, no-parity, 8-bit data length, no flow control.

- C. Timeout is 5 seconds.

For reference, the following settings are programmed into INFO0 on the Apollo510 SoC resident on the EVB:

- Secure Bootloader (SBL) interface is configured to UART0 using GPIO30 and GPIO55, which allows secure boot to be performed over the J-Link COM interface of the EVB.

- SBL override pin is configured to GPIO93 which is Button 0 (SW2) on the EVB.

For information on changing the INFO0 settings as well as using the Secure Bootloader, please refer to the README.txt file found in the tools\apollo510\_scripts folder of the latest SDK release supporting the Apollo5 family. This folder contains a number of python scripts to demonstrate generation of INFO0 settings, customer main images, and the creation of images for the Wired Update protocol over UART.

Please consult your Ambiq sales team for any additional documentation on INFO0 settings or Secure Bootloader, and visit the Content Portal for security documentation for the Apollo5 family.

# 7. Header Pin Assignments

This section provides an overview of the Apollo510 EVB connectivity and pin function options.

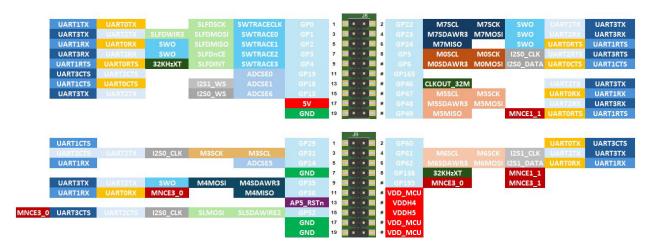

#### 7.1 MikroBUS Headers

The Apollo510 EVB provides a MikroBUS header to enable rapid prototyping. The interface is accessed through headers J14 and J15 as shown in Figure 6. Function options for the GPIO on the header pins are as shown.

Figure 6. J14/J15 MikroBUS Headers - Function Options

### 7.2 General Purpose Headers

Function options for pins of general purpose headers J8 and J9 are as shown in Figure 7.

Figure 7. J8/J9 General Purpose Headers - Function Options

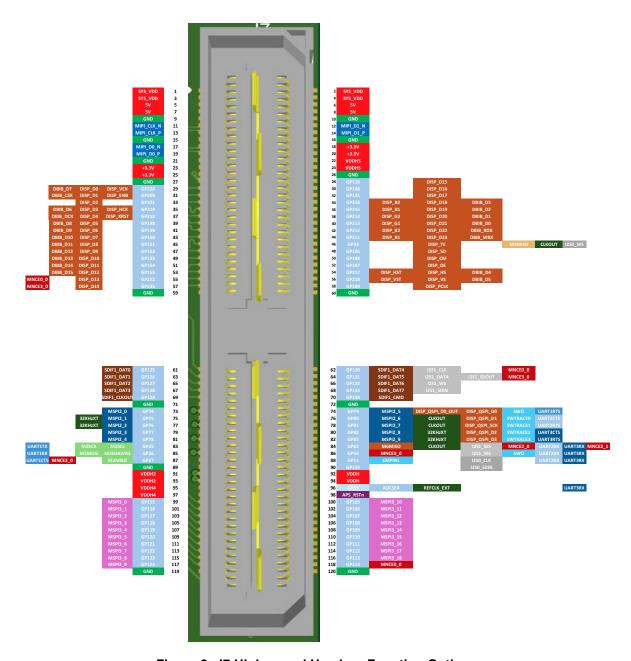

# 7.3 High-speed Header

Function options for pins of the high-speed header J7 are as shown in Figure 8.

Figure 8. J7 High-speed Header - Function Options

Figure 9 shows the board view of the J7 high-speed header which is located on the right edge of the EVB. The protective tape should be removed from the header before use.

Figure 9. Board View of J7 High-speed Header

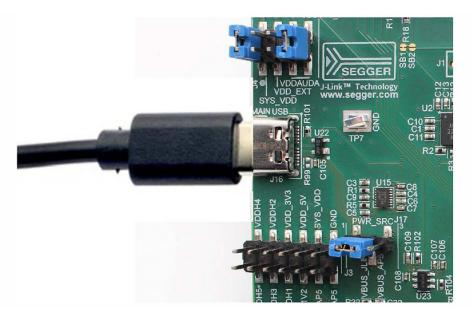

# 8. Debug Interface

Figure 10 shows the Apollo510 EVB set up for standard debug using the on-board J-Link debugger and on-board power supply.

Figure 10. Using On-board J-Link Debugger

The debug interface is supported by standard J-Link drivers from Segger. Please refer to "Software Development Tools" on page 17 for more details on J-Link debug support.

### 8.1 Use of External Debugger

This EVB also supports the use of an external SWD debug interface through a 20-pin debug-in header (DEBUG HDR – J2) as shown in Figure 11. See the EVB schematic for connector pinout.

Figure 11. J2 Debug-In Header

No jumper changes are required to use an external debug adapter. Simply connect the external debug adapter with a ribbon cable connector to the "DEBUG HDR" header.

**NOTE:** Remove protective guard before attempting to connect to the debug header.

# 9. Software Development Tools

The standard Segger J-Link debug interface is used on the Apollo510 EVB. Regardless of IDE used, please install the Segger J-Link software - see <a href="https://www.segger.com/downloads/jlink">https://www.segger.com/downloads/jlink</a>. Refer to the AmbiqSuite SDK for version numbers of the IDEs used for that release, and see the \AmbiqSuite\debugger\_updates\ folder in the AmbiqSuite SDK for interim updates for Keil, IAR, and JLINK.

#### **IMPORTANT NOTE**

When installing the Segger J-Link software described above, it may be necessary to select the "Install Legacy USB Driver" option in order to properly enable the USB connection. This option is not selected by default in the Segger installation setup dialog box, so the checkbox has to be checked to install the legacy USB driver. (This is the only default installation option that needs to be changed when installing the software.)

## 10. Power Supply Options and Measuring Current

The Apollo510 EVB is intended to operate off a 5 V supply, which is used to generate down-stream voltages.

There are three options for the main power supply (VDD\_MCU) for the EVB SoC:

- Operate at a nominal 1.8 V regulated down from the VDD\_5V supply to source the on-board power rail SYS\_VDD (default). Note that this voltage can be adjusted to 1.9 V by cutting SB3 shown on the Power Supplies page of the EVB schematic.

- Operate at 1.8 V via the low-noise VDD1V8 LN output of the regulated-down VDD 3V3 supply.

- Provide externally-supplied power via J6 (shown but not labeled) in Figure 12.

**NOTE:** If externally supplying VDD\_MCU and/or VDDAUDA, which powers the analog audio and XTALHS crystal of Apollo510, from VDD\_EXT, the supplied voltage range must be in the specified range for the rail(s) being supplied:

- If externally supplying VDD\_MCU and VDDAUDA, the allowable range is 1.71 V to 1.98 V.

- If supplying VDDAUDA from the VDD1V8\_LN regulated output and not by externally supplied VDD MCU, the allowable VDD EXT range is 1.71 V to 2.2 V.

- If externally supplying VDDAUDA but not VDD\_MCU, the allowable VDD\_EXT range is 1.62 V to 1.98 V.

Figure 12. J6 External Supply Header

The EVB utilizes jumpers for connecting and disconnecting rails from power supplies, whether generated on-board or off-board. The following figures show the jumper connection strategy among various on-board power supplies and the SoC's power rails.

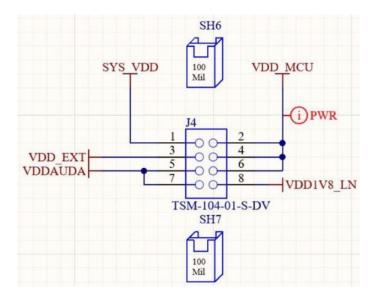

Figure 13 shows the power sourcing options for VDD MCU.

Figure 13. J4 Power Supply Jumper Connections

The J4 default jumper configuration is as shown in Figure 14 and in Table 2.

Figure 14. J4 Default Jumper Configuration

| Power Supply Source | From<br>Header Pin | To Header<br>Pin | Power Supply Destination |

|---------------------|--------------------|------------------|--------------------------|

| SYS_VDD             | J4-1               | J4-2             | VDD_MCU                  |

| VDD1V8_LN           | J4-8               | J4-7             | VDDAUDA                  |

**Table 2: J4 Default Jumper Configuration Table**

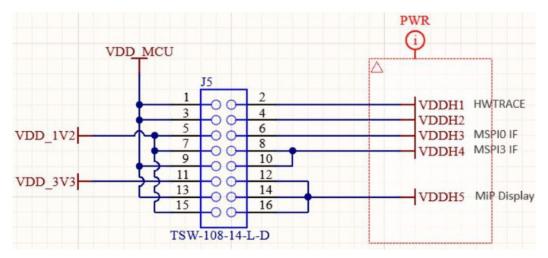

Figure 15 shows the power sourcing options for VDDH4 and VDDH5. VDDH1 and VDDH2 are always sourced from VDD\_MCU, and VDDH3 is always sourced from VDD\_1V2. VDDH4 can be sourced from VDD\_MCU or VDD\_1V2, and VDDH5 can be sourced from VDD\_MCU, VDD\_1V2 or VDD\_3V3.

Figure 15. J5 Power Supply Jumper Connections

The J5 default jumper configuration is as shown in Figure 16 and Table 3.

Figure 16. J5 Default Jumper Configuration

| Power Supply Source | From<br>Header Pin | To Header<br>Pin | Power Supply Destination |

|---------------------|--------------------|------------------|--------------------------|

| VDD_MCU             | J5-1               | J5-2             | VDDH1                    |

| VDD_MCU             | J5-3               | J5-4             | VDDH2                    |

| VDD_1V2             | J5-5               | J5-6             | VDDH3                    |

| VDD_MCU             | J5-9               | J5-10            | VDDH4                    |

| VDD_MCU             | J5-13              | J5-14            | VDDH5                    |

**Table 3: J5 Default Jumper Configuration Table**

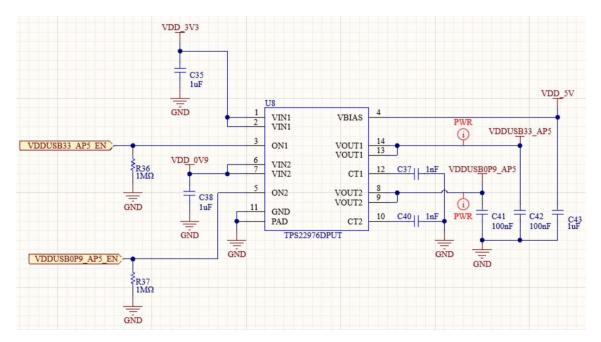

#### 10.1 USB and VDD18/MIPI Load Switch Circuits

Figure 17 shows the USB load switch circuit producing the voltage supplied to VDDUSB33\_AP5 and VDDUSB0P9 AP5.

Figure 17. USB Load Switch Circuit

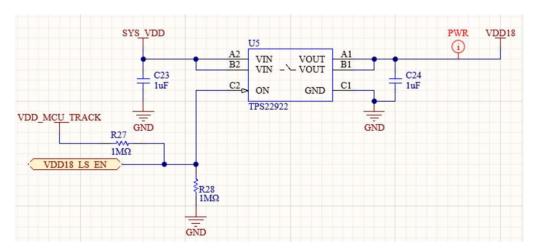

Similarly, Figure 18 shows the load switch circuit that produces the voltage supplied to the MIPI DPHY VDD18.

Figure 18. VDD18/MIPI Load Switch Circuit

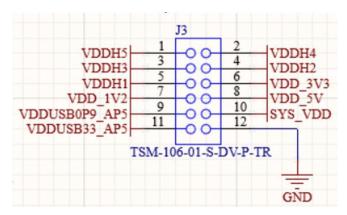

#### 10.2 Monitoring or Externally Supplying Supply Voltages

As shown in Figure 19 and Figure 20, header J3 provides easy access to the various system and chiplevel power supplies present on the EVB. These can be used to monitor voltage or provide externally generated power to each specific rail after assuring that the on-board supply has been disconnected.

Figure 19. J3 Voltage Test Points Header

Figure 20. Board View of J3 Voltage Test Points Header

# 10.3 Measuring Current

Current consumption of the Apollo510 EVB can be measured by connecting an ammeter between the corresponding DUT supplies. Refer to Figure 12 or Figure 15 to measure the current draw from the power supply of interest. Before using an ammeter, turn the power off, remove the corresponding jumper and install the ammeter properly prior to powering the board back on. When the current measurements have been completed, reposition the jumper at its former location.

# 11. Ordering Information

| Device Name   | Orderable<br>Part Number | EVB Revision | SoC           |

|---------------|--------------------------|--------------|---------------|

| Apollo510 EVB | AP510EVB                 | 2.2          | Apollo510 BGA |

**Table 4: EVB Ordering Information**

| Device<br>Name <sup>a</sup> | Commercial<br>Temp Range<br>(-20°C to<br>70°C) | Package<br>Type | GPIOs | NVM<br>(MRAM) | SRAM    | Package <sup>b</sup> Size<br>(mm) |

|-----------------------------|------------------------------------------------|-----------------|-------|---------------|---------|-----------------------------------|

| Apollo510<br>SoC            | AP510NFA-<br>CBR                               | BGA             | 183   | 4 MB          | 3.75 MB | 6.6 x 6.6 x 0.75<br>225-pin BGA   |

| Apollo510<br>SoC            | AP510NFA-<br>CCR                               | WLCSP           | 144   | 4 MB          | 3.75 MB | 4.9 x 4.7<br>182-pin WLCSP        |

Table 5: Apollo510 SoC Ordering Information

a. The silicon revision is identified by the first letter in the bottom row of the package's top marking.

b. Packing: Tape and Reel

©2025 Ambiq Micro, Inc. All rights reserved.

Ambiq Micro, Inc.

6500 River Place Boulevard, Building 7,

Suite 200, Austin, TX 78730-1156

www.ambiq.com/

sales@ambiqmicro.com

https://support.ambiqmicro.com

+1 (512) 879-2850

QS-A510-2p1

Version 2.1

November 2025